# PRELIMINARY

105

3 PARALLEL AND 2 SERIAL I/O INTERFACE

USER'S MANUAL

SSM MICROCOMPUTER PRODUCTS, INC. 2190 Paragon Drive San Jose, California 95131

Telephone: (408) 946-7400

## 105 TABLE OF CONTENTS

- 1.0 INTRODUCTION

- 2.0 SEITING UP YOUR 105

- 2.1 Addressing the Board 2.1.1 I/O Boundary 2.1.2 Status/Data Order

- 2.2 Serial Interfaces

- 2.2.1 Baud Rate Selection

- 2.2.2 Interfacing a Modem2.2.3 Interfacing a Terminal2.2.4 Software Information

- 2.2.5 Serial Interrupts

- 2.3 Programmable Parallel Interface 2.3.1 Interface Connections 2.3.2 Software Information

- 2.4 Parallel Input 2.4.1 Interface Connections 2.4.2 Software Information

- 2.5 Parallel Output 2.5.1 Interface Connections 2.5.2 Software Information

- 2.6 Timer 2.6.1 Jumper Options

- 2.6.2 Software Examples

- 2.7 Interrupt Circuit

- 2.7.1 Introduction 2.7.2 Pass Data Codes

- 2.7.3 CPU Interrupt Line 2.7.4 Board Arbitration

- - 2.7.4.1 Daisy Chain

- 2.7.4.2 VI Lines

- 2.7.4.3 Address Lines

- 2.8 High-Speed Parallel Link

- 3.0 THEORY OF OPERATION

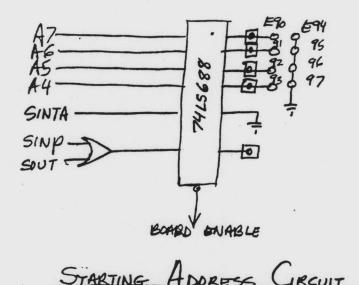

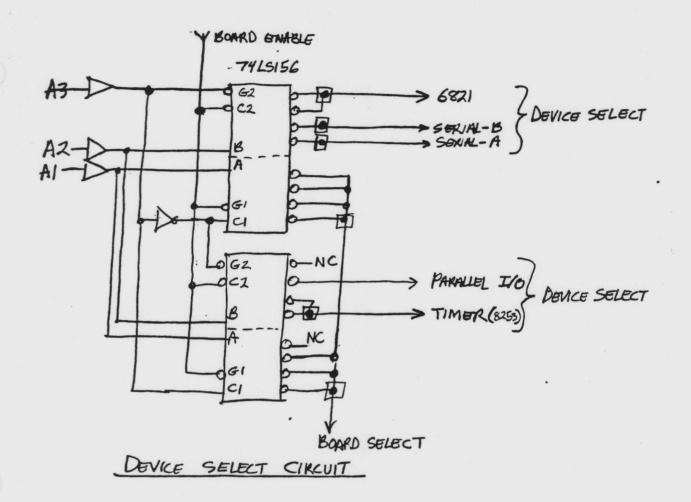

- 3.1 Address Select Circuit

- 3.2 E-signal to 6821 Chip

- 3.3 Wait Circuit

- 3.4 Serial Control 3.5 Baud Rates

- 3.6 Parallel Input 3.7 Parallel Ouput 3.8 Interrupt Circuit

1

# 4.0 TROUBLESHOOTING HINTS

5.0 WARRANTY

APPENDIX:

Assembly Diagram Jumper Diagram Parts List Schematic (INSERT)

Intel 8251A Specification Sheet

6821B Specification Sheet 8253 (MC14411) The IO5 serial and parallel I/O card provides extremely flexible interfacing for your S-100 or new IEEE 696 systems. Two serial and 3 parallel input/output ports support a wide variety of devices such as:

- o Terminals

- o Modems

- o Serial and parallel printers

- o Keyboards

- o Card readers

Multiple boards can be used to support systems requiring a large number of peripherals for a wide variety of multi-user applications:

- o Special purose business applications (word processing, hotel management, banking terminals, training systems)

- o Real-time control systems (engraving, machine tools, robotics, energy management

- o Data collection (quality control, laboratory data acquisition, communications message switching)

- o Add-in/upgrading of current S-100 systems (Nothstar, Dynabyte, Cromemco, Ithaca)

Baud rates are individually selectable for 110 to 19,200 baud. Each serial interface is accessible from the bus as 110 in a status/data port pair. Serial interfaces can be set through software for:

o 5 to 8 data bits o 1 or 2 stop bits o parity enable o parity even or odd o sending a break character o control the RTS and DTR

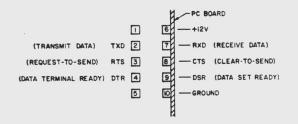

Seven standard signals are provided on the RS232 connector for each serial interface:

TD (Transmit Data) RD (Receive Data) RTS (Request-To-Send) CTS (Clear-To-Send) DTR (Data Terminal Ready) DSR (Data Set Ready) SG (Signal Ground)

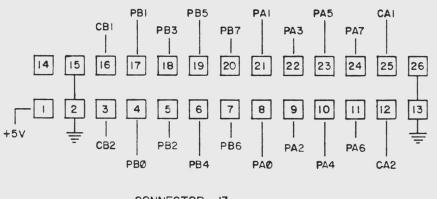

A 6821B PIA provides two 8-bit bidirectional parallel I/O ports. The 26 pin connector, J3, can be two 8-bit I/O ports or one 16-bit I/O port. Each of the peripheral data lines can be individually programmed to be input or output. Each of the four control/interrupt lines can be programmed for one of several control modes. These features allow a high degree of flexibility:

o Two 8-bit bidirectional I/O ports

o Two programmable control registers

- o Two programmable data direction registers o Four individually controlled interrupt lines

- o Handshaking

- o Program-controlled interrupt and interrupt disable capability

Optional cable assemblies are available for terminal printer or modem interfacing.

# 2.0 SETTING UP YOUR IO5

# 2.1 ADDRESSING THE BOARD

# 2.1.1 I/O Boundary

The IO5 board looks like 14 I/O ports to the main CPU. The 14 I/O ports can be addressed to start at any 16-port boundary by jumpers E90 thru E97. Refer to the following table:

Mini-jumper installed = J (Jumper) Mini-jumper removed = N (No connection)

| I/O STARTING<br>ADDRESS<br>(Hex) | <b>E90</b><br>to<br><b>E94</b> | <b>E9</b> 1<br>to<br><b>E9</b> 5 | <b>E9</b> 2<br>to<br><b>E96</b> | <b>E9</b> 3<br>to<br><b>E97</b> |

|----------------------------------|--------------------------------|----------------------------------|---------------------------------|---------------------------------|

| 00                               | J                              | J                                | J                               | J                               |

| 10                               | J                              | J                                | J                               | N                               |

| 20                               | J                              | J                                | N                               | J                               |

| 30                               | J                              | J                                | N                               | N                               |

| 40                               | J                              | N                                | J                               | J                               |

| 50                               | J                              | N                                | J                               | N                               |

| 60                               | J                              | N                                | N                               | J                               |

| 70                               | J                              | N                                | N                               | N                               |

| 80                               | N                              | J                                | J                               | J                               |

| <b>9</b> 0                       | N                              | J                                | J                               | N                               |

| AO                               | N                              | J                                | N                               | J                               |

| B0                               | N                              | J                                | N                               | N                               |

| CO                               | N                              | N                                | J                               | J                               |

| D0                               | N                              | N                                | J                               | N                               |

| EO                               | N                              | N                                | N                               | J                               |

| FO                               | N                              | N                                | N                               | N                               |

The 14 I/O ports can be further broken down into the functions within the IO5 by the following table:

X = Starting address selected by E90 thru E97

| ADDRESS<br>(Hex) | FUNCTION                                                   |

|------------------|------------------------------------------------------------|

| X0, X1           | Serial-A interface, Jl connector<br>(8251A chip used)      |

| X2, X3           | Serial-B interface, J2 connector<br>(8251A chip used)      |

| X4, X5           | Programmable parallel-A, J3 connector<br>(6821B chip used) |

| X6, X7           | Programmable parallel-B, J3 connector<br>(6821B chip used) |

| X8     | Programmable timer, counter 0<br>(8253 chip used)    |

|--------|------------------------------------------------------|

| X9     | Programmable timer, counter 1                        |

| XA     | Programmable timer, counter 2                        |

| XB     | Programmable timer, control port                     |

| XC, XD | Parallel input , J4 connector<br>(8212 chip used)    |

| XC, XD | Parallel ouput , J5 connector<br>(74LS273 chip used) |

# 2.1.2 Status/Data Order

The serial and parallel interfaces on the IO5 have status and data port pairs which can be reversed by jumper E56 thru E58. Some system standards require a status port first (even address) with the data port following (odd address). All status and data port addresses, except the timer function, are affected by this jumper.

Status port (even address), data port (odd address) Jumper E57 to E58

Data port (even address), status port (odd address) Jumper E56 to E57

This jumper selection MUST BE MADE for the board to work properly.

# 2.2 SERIAL INTERFACES

#### 2.2.1 Baud Rate Selection

The serial channels can be strapped for any one of 8 baud rates from 110 to 19200 baud. A 16-pin socket on the IO5 is used for an IC header to make the baud rate selection; just run a connection from the Serial-A or B clock pin to the speed desired (110 up to 19200).

NOTE: Only one baud rate should be jumpered per serial clock pin.

| 0 0         | E 106 (SERIAL-A CLOCK INPUT, BRØ)                   |

|-------------|-----------------------------------------------------|

| 0 0         | EIO7 (SERIAL-B CLOCK INPUT, BRI)                    |

| 0 0         | EIOB                                                |

| 0 0         | EIO9                                                |

| 20 0        | EIIO                                                |

| 30 0        | EIII                                                |

| 40 O        | EII2                                                |

| 50 <b>0</b> | E113                                                |

|             | 0  0  0    0  0  0    1  0  0    2  0  0    3  0  0 |

To set the baud rate for Serial-A, strap El06 on an IC header (16-pin) to **CNE** of 8 rates on pins E98 thru El05.

To set the baud rate for Serial-B, strap El07 on an IC header (16-pin) to **CNE** of 8 rates on pins E98 thru El05.

# 2.2.2 Interfacing a Modem

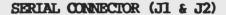

The two serial interfaces (A and B) on the IO5 come off to a 10-pin male ribbon cable connector. Each connector provides six RS-232 signals and signal ground for terminal or modem applications.

The interconnection from this 10-pin connector to a DB25 connector for a modem would be as follows:

Frame ground normally connects to the chassis ground of the computer mainframe, while signal ground for the DB25 connector comes from the 10-pin serial connector.

To make this interconnection easier, SSM has an optional modem adapter cable (SSC-02) for use with the IO5 board. The modem adapter has a two-foot mating cable for the IO5's serial connector with a DB25 socket.

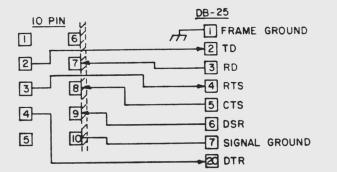

## 2.2.3 Interfacing a Terminal

The two serial interfaces (A and B) on the IO5 come off to a 10-pin male ribbon cable connector. Each connector provides six RS-232 signals and signal ground for terminal or modem applications. (Refer to the SERIAL CONNECTOR figure in Section 2.2.2 for pin-out).

To interface with a terminal, the 10-pin connector will be connected to a DB25 connector as follows:

Frame ground normally connects to the chassis ground of the computer mainframe, while signal ground for the DB25 connector comes from the 10-pin serial connector.

To make this interconnection easier, SSM has an optional terminal adapter cable (SSC-03) for use with the IO5 board. The terminal adapter has a two-foot mating cable for the IO5's serial connector with a DB25 socket.

# 2.2.4 Software Information

For more detailed information on the 8251A and its modes of operation, refer to the Intel specification sheet in the APPENDIX.

The 8251A uses two I/O ports for its communication and command. The ports can be switched around by jumpers E56 thru E58.

Jumper E57 to E58

| ADDRESS<br>(Hex) FUNCTION | INTERFACE |

|---------------------------|-----------|

| 0 Status/command          | A         |

| 1 Data in/out             | A         |

| 2 Status/command          | В         |

| 3 Data in/out             | В         |

#### JUMPER E56 to E57

ADDRESS

| (Hex) | FUNCTION       | INTERFACE |

|-------|----------------|-----------|

| 0     | Data in/out    | A         |

| 1     | Status/command | BA        |

| 2     | Data in/out    | В         |

| 3     | Status/command | В         |

On hardware reset (bus) or internal reset (software), the 8251A needs a mode byte entered into its command port to set the asynchronous data format. The mode byte format is as follows:

| D7       |                       | NUMBER OF                   | STOP BITS                    |                            |

|----------|-----------------------|-----------------------------|------------------------------|----------------------------|

|          | 0                     | 0                           | 1                            | 1                          |

| D6       | 0                     | 1                           | 0                            | 1                          |

| 00       | Invalid               | 1 bit                       | 1.5 bits                     | 2 bits                     |

| D5       | Parity stat           | e, 0=odd,                   | 1=even                       |                            |

| D4       | Parity_enab           | le, O=dis                   | able, 1=enab                 | le                         |

|          |                       | CILADACTE                   |                              |                            |

|          |                       | CHARACIE                    | R LENGTH                     |                            |

| D3       | 0                     | 0                           | R LENGTH<br>1                | 1                          |

|          | 0                     | 0<br>1                      | R LENGTH<br>1<br>0           | 1                          |

| D3<br>D2 | 0<br>0<br>5 bits      | 0<br>1<br>6 bits            | R LENGTH<br>1<br>0<br>7 bits | 1<br>1<br>8 bits           |

| D2       | 0<br>0<br>5 bits      | 0<br>1<br>6 bits            | 1<br>0                       | 1<br>1<br>8 bits           |

|          | 0<br>0<br>5 bits<br>0 | 0<br>1<br>6 bits            | 1<br>0<br>7 bits             | 1<br>1<br>8 bits<br>1      |

| D2       |                       | 0<br>1<br>6 bits<br>BAUD RA | 1<br>0<br>7 bits             | 1<br>1<br>8 bits<br>1<br>1 |

01001110 = 4 E

#### NODE BYTE FORMAT

The IO5's baud rate generates 16 times the data bit clock rate, so D0=0 and D1=1. Typical character length is 8 bits, so D2=1 and D3=1. Parity selection will vary with the interfacing equipment and hardware application. If baud rates above 300 are selected, 1 stop bit is typical, and D6=1 and D7=0. Therefore, a standard byte could be 4E Hex in most applications.

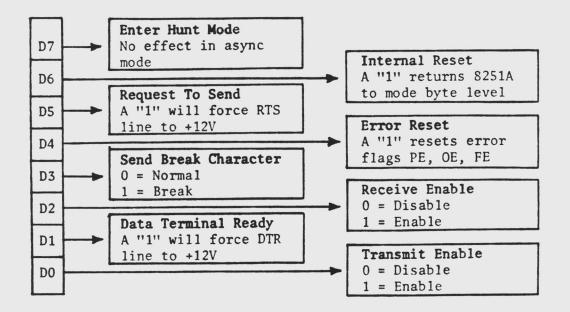

Once the mode byte is entered, a command byte should be sent. This byte will control the RS-232 handshaking lines DTR and RTS, enable transmit and receive modes, clear error flags, send a "break" character, or reset back to the mode byte level.

and RTS, and a "break" chan 01001110 = 4F given 16X BAUD = 30064X BAUD = 1200

#### COMMAND BYTE FORMAT

A typical command byte would enable receive and transmit functions, force RTS and DTR high, not send a break character to start, and leave the error flags enabled for any possible communication problems. The command byte should be 27 Hex in most cases.

The same port address that a mode or command byte is written to the 8251A is also the status port for normal communication. This port will indicate the arrival of data and the completion of transmisson of data.

#### STATUS BYTE FORMAT

| D7 | 1 = | DSR | line | is | high |

|----|-----|-----|------|----|------|

|----|-----|-----|------|----|------|

- D6 Don't care

- D5 1 = Framing error detected (no stop bit)

- D4 1 = Overrun error detected (buffer overflow)

- D3 1 = Parity error detected

- D2 1 = Transmit buffer empty

- Dl l = Data received (data available)

- D0 1 = Transmit buffer ready (acknowledges sending)

If interrupts are used on the Serial-A and Serial-B interface by strapping the INTERRUPT PRIORITY header, then masking these interrupts will become important. Bits 0 and 2 in the control byte are the interrupt mask bits. The 8251A has two output pins (RXRDY and TXRDY) which are "OREd" into one common interrupt line to the INTERRUPT PRIORITY header.

#### SERIAL INTERRUPTS

o RXRDY line is true:

- . Receive enable bit must be true (enable).

- . Receive buffer has a character.

NOTE: Receive enable bit must be true to sense the start bit on an incoming character.

o TXRDY line is true:

- . Transmit enable bit must be true (enable).

- . CTS input line must be greater than +3 volts.

- . Transmit buffer is empty.

If either output line (RXRDY or TXRDY) is true, an interrupt can be generated. Software must check the status byte to determine if the interrupt is for receiving or transmitting.

# EXAMPLE SOFTWARE

Serial-A for simple I/O with no interrupts. Jumper E57 to E58 installed and board address set to 00 Hex.

|                   | and board address                    |                                             |                                              |                                                  |                                      |

|-------------------|--------------------------------------|---------------------------------------------|----------------------------------------------|--------------------------------------------------|--------------------------------------|

| RESIDENC          | ; PORT ADDRESSES<br>KSTAT<br>KDATA   | EQU<br>EQU                                  | 0<br>1                                       | ;STATUS/COMMAND PORT<br>;DATA PORT               |                                      |

| JNINGS            | ;LOCATION OF EXALLOC                 | MPLE DR<br>EQU                              |                                              | USER DEFINED ADDRESS                             |                                      |

| 5                 |                                      | ORG                                         | LOC                                          |                                                  |                                      |

| 10/2              |                                      | JMP<br>JMP<br>JMP                           | INTZ<br>GET<br>PUT                           | ; INITIALIZE 8251<br>;GET DATA<br>;SEND DATA     |                                      |

| 22                | ; INITIALIZATION                     | ROUTINE                                     |                                              | 31                                               |                                      |

| Syould INITIALIZE | ;HELP GUARANTEE '<br>INTZ:<br>INTZ1: | THE STA'<br>MVI<br>XRA<br>OUT<br>DCR<br>JNZ | TE OF THE<br>B,3<br>A<br>KSTAT<br>B<br>INTZ1 | SEND DATA<br>SEND DATA<br>8251 PART<br>SEND Ø TO | 06 03<br>AF<br>D3 30<br>05<br>c2 000 |

|                   | AT THIS POINT T                      |                                             |                                              | NITELY WAITING FOR A COMMAND BYTE                | 32 40                                |

| 229807            |                                      | MVI<br>OUT                                  | A,40H<br>KSTAT                               | RESET TO MODE LEVEL                              | D3 30                                |

| 107               |                                      |                                             | A, 4EH<br>KSTAT                              | ; MODE BYTE                                      | 3E 4E<br>DE 30                       |

| 14.41             |                                      |                                             | A,37H<br>KSTAT                               | ;COMMAND + ERROR RESET                           | 32 42<br>D3 30                       |

| 800757890         |                                      |                                             | 11                                           |                                                  |                                      |

| 8                 |                                      |                                             | 11                                           |                                                  |                                      |

| MVI<br>OUT<br>RET                                 | <b>A, 27</b> H<br>KSTAT | ; COMMAND  | 35 27<br>D3 30                 |

|---------------------------------------------------|-------------------------|------------|--------------------------------|

| ; INPUT ROUTINE, REGA=<br>; EXITS WITH: A=DATA RI |                         |            | 100H DB 30                     |

| GET: IN                                           | KSTAT                   | GET STATUS | DB 72                          |

| ANI                                               | 2                       | ; TEST DAV | CA ODOI                        |

| JZ<br>IN                                          | GET<br>KDATA            | ;GET DATA  | DB 31                          |

| RET                                               |                         |            | 4F                             |

| ;OUTPUT ROUTINE, REGC                             |                         | MONGA      |                                |

| ;ENTER WITH: C=DATA TO                            |                         |            | DD DB 30                       |

| PUT: IN<br>ANI                                    | KSTAT<br>4              | GET STATUS | 56 04                          |

| JZ                                                | PUT                     |            | 200 PB 30<br>26 04<br>CA 00 02 |

In writing other software for the 8251A, you must have greater than 3.26 microseconds between writes during initialization; 4.34 microseconds between writes once in asynchronous mode; and 8.68 microseconds between writes if the part is running synchronous.

;SEND DATA

m9 D3 31

C3 00 01

TIMING CONTS

#### 2.2.5 Serial Interrupts

MOV

OUT

RET

A,C

KDATA

The interrupt signals for DAV (Data Available) and DAK (Data Acknowledge) for each serial interface (A thru H) are sent to an INTER-RUPT PRIORITY header U51. Each serial interrupt can be jumpered to the priority desired (0 thru 7) or not connected if no interrupts are desired.

Only one serial interrupt signal can be tied to a particular priority level on U51 (i.e., you cannot connect two or more serial interrupts to one priority level input).

It may be desirable to have interrupts on serial inputs, but none on the DAK signal for serial outputs. The ability to send serial data, but not generate an interrupt, is possible with the 8251A under software. The TX-ENABLE bit in the command byte to the 8251A must be zero until a byte to be transmitted is loaded into the 8251A. With TX-ENABLE bit low, no DAK interrupt will be sent. Now fill the output buffer in the 8251A, and again no DAK interrupt will be sent. Next, with the buffer full, set TX-ENABLE bit equal to a one in the command byte; then immediately set TX-ENABLE bit low again. This change of state of the TX-ENABLE bit will cause transmission of the serial data without allowing the DAK interrupt.

An example routine for initializing the 8251A, checking DAK status, outputting serial data, enabling interrupts on DAK, and disabling interrupts on DAK in 8080 code follows.

# 2.3 PROGRAMMABLE PARALLEL INTERFACE

# 2.3.1 Interface Connections

The parallel interface to connector J3 uses a 6821B IC (U6). This part has 8-bit bidirectional data ports, and each port has two 1-bit handshaking lines for hardware protocol. The 26-pin connector (J3) has been set up so that the ribbon cable can be split down the middle for two 8-bit interfaces or not split for a 16-bit data interface.

The 6821B specification sheet designates the two 8-bit interfaces as "A" and "B". PA and PB are the data lines, with CA and CB the handshaking lines. The B-side of the connector J3 has been provided with +5 volts with up to 100 milliamperes of current for any special external support circuitry that may be needed for the user's application.

CONNECTOR J3

For further information on the capability of the 6821B, refer to the specification sheet in the APPENDIX.

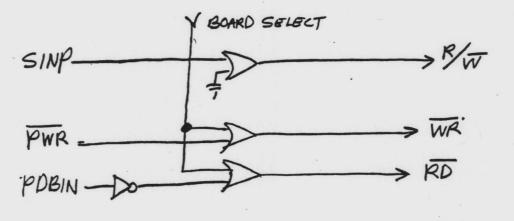

Unique to the programmable parallel interface is a timing signal called "E". The E-signal is generated on the IO5 board every time the CPU is reading (PDBIN is high) or writing (PWR is low) to strobe an internal function within the 6821B IC (U6). The width of the E-signal is processor-dependent and related to the phase 2 signal (bus pin 24). The E-signal can be changed in width by one-half a cycle through the setting of a jumper from E53 to E54 or E54 to E55.

| CPU  | JUMPER     |

|------|------------|

| CB2  | E54 to E55 |

| CBLA | E54 to E55 |

If not jumpered correctly, the handshaking lines (CA1, CA2, CB1 & CB2) on the 6821B will not respond correctly.

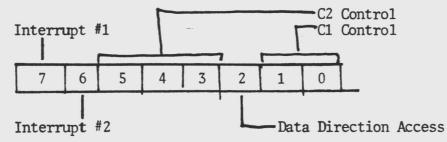

## 2.3.2 Software Information

The 6821B chip occupies four I/O ports on the IO5 board. As listed in Section 2.1.2, two ports for the "A" interface are at X4 and X5, while

two ports for the "B" interface are at X6 and X7. The port pairs are divided into a status/control port and a data port. The status/control port may be the first port of a pair addressed depending on the setting of the jumper in Section 2.1.2.

#### Jumper E57 to E58

#### ADDRESS (Hex) FUNCTION

| X4         | Status/control port-A |

|------------|-----------------------|

| <b>X</b> 5 | Data/direction port-A |

| X6         | Status/control port-B |

| X7         | Data/direction port-B |

#### Jumper E56 to E57

| ADDRESS<br>(Hex) | FUNCTION              |

|------------------|-----------------------|

| X4               | Data/direction port-A |

| <b>X</b> 5       | Status/control port-A |

| X6               | Data/direction port-B |

| X7               | Status/control port-B |

On power-up or reset of the computer system, the status/control should be set to 00 Hex. Next, the data direction for the A and B interfaces should be programmed by writing out to the data ports of the 6821B. A "0" bit sets the corresponding data line as an input while, a "1" bit sets the line as an output.

After the data direction has been preset, the status/control port should be set to the desired mode and bit 2 set to a logic 1.

The status/control ports for A and B are broken down into control bits as follows:

The Cl control bits (1 and 0) set the interrupt mode of the CBl (or CAl) inputs on the 6821B chip.

| BIT 1 | BIT O | INPUT CBL<br>(or CA1)     | INT #1 FLAG | INT REQUEST                   |

|-------|-------|---------------------------|-------------|-------------------------------|

| 0     | 0     | High to low transition    | Set high    | Disable Intr 2<br>(or Intr 3) |

| 0     | 1     | High to low transition    | Set high    | Enable Intr 2<br>(or Intr 3)  |

| 1     | 0     | Low to high<br>transition | Set high    | Disable Intr 2<br>(or Intr 3) |

| 1     | 1     | Low to high<br>transition | Set high    | Enable Intr 2<br>(or Intr 3)  |

The ability to sense a pulse on the CBl (or CAl) inputs is controlled by the "E" line on the 6821B. The rate at which the main CPU reads or writes to the 696 bus is turned into an enable signal (E line) for the 6821B. The pulse on the CBl (or CAl) inputs must be wider than the time between CPU reads and writes. In most cases a pulse of 2 microseconds or greater will be acceptable.

The C2 control bits (5, 4, and 3) sets the CB2 (or CA2) as inputs or output lines on the 6821B chip.

As an Input (Bit 5 = 0)

| BIT 4 | BIT 3 | INPUT CB2<br>(or CA2)     | INT #2 FLAG | INT REQUEST                   |

|-------|-------|---------------------------|-------------|-------------------------------|

| 0     | 0     | High to low<br>transition | Set high    | Disable Intr 2<br>(or Intr 3) |

| 0     | 1     | High to low transition    | Set high    | Enable Intr 2<br>(or Intr 3)  |

| 1     | 0     | Low to high transition    | Set high    | Disable Intr 2<br>(or Intr 3) |

| 1     | 1     | Low to high transition    | Set high    | Enable Intr 2<br>(or Intr 3)  |

| BIT<br>4 | BIT<br>3 | CLEARED                                                                             | SET                                                                                        |

|----------|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 0        | 0        | Goes low on the first<br>"E" pulse following an<br>output of data to the<br>B-port. | Goes high when the INT #1<br>flag is high by an active<br>transition of the CB1<br>signal. |

| 0        | 1        | Goes low on the first<br>"E" pulse following an<br>output of data to the<br>B-port. | Goes high on the first "E"<br>which occurred while the<br>part was not addressed.          |

| 1        | 0        | Output equals the state of Bit 3.                                                   | Output equals the state of Bit 3 (Output = $0$ ).                                          |

| 1        | 1        | Output equals the state of Bit 3.                                                   | Output equals the state of Bit 3 (Output = $0$ ).                                          |

|          |          |                                                                                     |                                                                                            |

Although only port B is listed in the output table, this table also applies to port A.

## EXAMPLE SOFTWARE

We will set up the 6821B as a simple I/O port. Port A will be an input and port B will be an output.

Jumper E57 to E58 installed and board address set to 00 Hex.

| ; PORT | ADDRESSES |    |          |  |

|--------|-----------|----|----------|--|

| CIRLA  | EQU       | 04 |          |  |

| DATAA  | EQU       | 05 | ; PORT A |  |

| CIRLB  | EQU       | 06 |          |  |

| DATAB  | EQU       | 07 | ; PORT B |  |

|        |           |    |          |  |

;LOCATION OF EXAMPLE DRIVER LOC EQU 0E000H

|          | ORG      | LOC     |        |        |     |         |

|----------|----------|---------|--------|--------|-----|---------|

|          | JMP      | INTZ    | ; INIT | TALIZE | 682 | 21B     |

|          | JMP      | PORTA   |        |        |     |         |

|          | JMP      | PORTB   |        |        |     |         |

| ; INITIA | LIZATION | ROUTINE | 2      |        |     |         |

| INTZ:    | XRA      | A       |        |        |     |         |

|          | OUT      | CIRLA   |        |        |     |         |

|          | OUT      | CIRLB   |        |        |     |         |

|          | MVI      | A,0     |        |        |     |         |

|          | OUT      | DATAA   | ;SET   | PORI-A | AS  | INPUTS  |

|          | MVI      | A, OFFH |        |        |     |         |

|          | OUT      | DATAB   | ;SET   | PORI-B | AS  | OUTPUTS |

|          | MVI      | A,4     |        |        |     |         |

|          |          |         |        |        |     |         |

|        | OUT       | CIRLA    | ; SWITCH  | OFF  | DIRECTION | BIT |

|--------|-----------|----------|-----------|------|-----------|-----|

|        | OUT       | CIRLB    |           |      |           |     |

|        | RET       |          |           |      |           |     |

|        | ; INPUT I | PORT DAT | A TO REA  | GA   |           |     |

| PORTA: | IN        | DATAA    | ; INPUT ] | PORT | DATA      |     |

|        | RET       |          |           |      |           |     |

|        | ;OUTPUT   | PORT DA  | TA FROM   | REG. | -A        |     |

| PORIB: | OUT       | DATAB    | ;OUTPUT   | DAT  | A TO PORT |     |

|        | RET       |          |           |      |           |     |

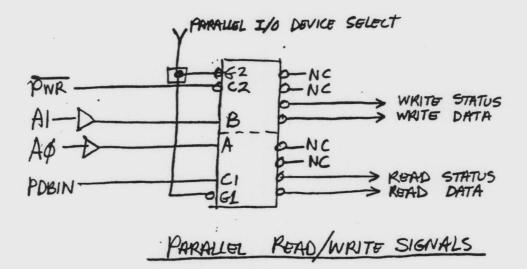

#### 2.4 PARALLEL INPUT

# 2.4.1 Interface Connections

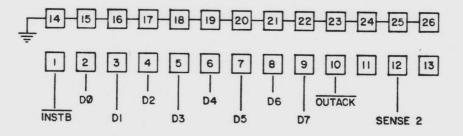

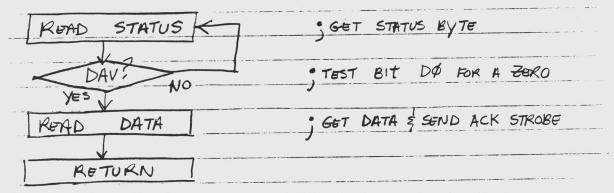

The parallel input interface to connector J4 uses a 8212 latch (U8). This part is well suited as an input interface because it has an internal flip-flop which can be used for handshaking between the main CPU and an external device. The connector J4 is a 26-pin version with alternate grounds running between each signal line.

CONNECTOR J4

#### 2.4.2 Software Information

The parallel input occupies two I/O ports on the IO5 board. The port pair is divided into a status port and a data port. The status port may be the first port of a pair addressed depending on the setting of the jumper in Section 2.1.2.

Jumper E57 to E58

| ADDRESS<br>(Hex) | FUNCTION |      |  |

|------------------|----------|------|--|

| XC               | Status   | port |  |

XD Data port

#### Jumper E56 to E57

#### ADDRESS (Hex) FUNCTION

| XC | Data port   |

|----|-------------|

| XD | Status port |

Data is entered into this input interface on a negative-going pulse (high to low) on the INSTB line. A flag (data available) is set for the CPU to read on the trailing edge of the pulse (low to high). If the flag is set, the OUTACK line (pin 10) will be high, indicating that data has been loaded into the 8212. The OUTACK line will only go low when the CPU has read the 8212, thus acknowledging the fetch of the data byte to the outside world. (The OUTACK line is also low when the IO5 is reset.)

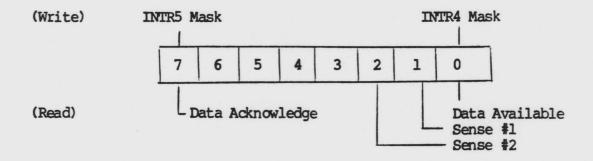

The input interface also has one input sense line which can be read through the status port as bit 2. A high on the sense input will be indicated as a low on bit 2 of the status port.

The data available flag can also provide an interrupt (INTR4) through the interrupt circuitry on the IO5 to the main CPU. This interrupt is maskable and is disabled on reset of the IO5. Bit 0 of the status port controls the mask bit and reads the data available flag.

#### READ STATUS

#### BIT 0 COMMENT

- 0 Data has been loaded into the input port (interrupt generated, if not masked).

- 1 No data available at the input port.

#### WRITE STATUS

- BIT O COMMENT

- 0 Mask out interrupt signal (interrupt disables on reset of IO5).

- 1 Enable interrupt signal (INTR 4).

#### STATUS BYTE

The input interface (J4) is compatible with the output interface (J5); with two IO5s and two 26-conductor ribbon cables, a high speed data link can be set up between two S-100 computers (see Section 2.8 for application).

#### EXAMPLE SOFTWARE

Data is received in the A-Register. Jumper E57 to E58 installed.

; PORT ADDRESSES KSTAT EQU OCH KDATA EQU ODH

;LOCATION OF EXAMPLE DRIVER LOC EQU 0E000H

| IPORT: | ORG<br>IN | LOC<br>KSTAT |

|--------|-----------|--------------|

|        | ANI       | 1            |

|        | JNZ       | IPORT        |

|        | IN        | KDATA        |

|        | RET       |              |

#### 2.5 PARALLEL OUTPUT

#### 2.5.1 Interface Connections

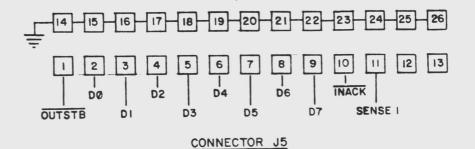

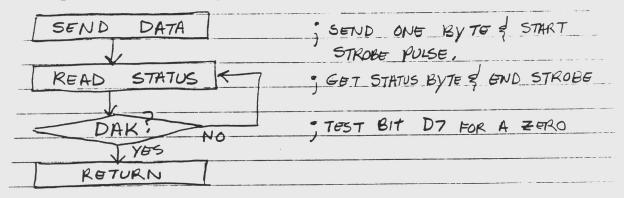

The parallel output interface to connector J5 uses a 74LS273 OCTAL D-FLIP FLOP (U10). This part had to be supplemented with an external flip-flop (U11) to provide two handshaking lines. The connector J5 is a 26-pin connector with alternate grounds running between signal lines. J5 is set up so that it is pin-compatible with a Centronics-type parallel printer device.

#### 2.5.2 Software Information

The parallel input occupies two I/O ports on the IO5 board. The port pair is divided into a status port and a data port. The status port may be the first port of a pair addresed depending on the setting of the jumper in Section 2.1.2.

Jumper E57 to E58

# ADDRESS

| UDEA/ | FORCITON |  |

|-------|----------|--|

|       |          |  |

| XC | Status port |

|----|-------------|

| XD | Data port   |

Jumper E56 to E57

| ADDRESS<br>(Hex) | FUNCTION  |  |  |

|------------------|-----------|--|--|

| XC               | Data port |  |  |

XD Status port

Data is output by simply writing the byte to the data port. When data is placed into the 74LS273 it also clocks a flip-flop to provide a lowgoing signal on the OUTSTB line. OUTSTB is used to strobe data into some external device interfaced to J5. To finish the pulse on OUTSTB, the status port must be read which will set OUTSTB back to a one. (The OUTSTB line is also low when the IO5 is reset).

The output interface also has one input sense line which can be read through the status port as bit 1. A high on the sense input will be indicated as a low on bit 1 of the status port.

The output interface has an acknowledge line whereby the external device can signal that it has received the data from the output. The acknowledge flag is cleared when data is placed into the output, and is set when a negative acknowledge place is sent back by the external device. (The acknowledge flag is set when the IO5 is reset.)

The acknowledge flag can also provide an interrupt (INTR 5) through the interrupt circuitry on the IO5 to the main CPU. This interrupt is

maskable and is disabled on reset of the IO5. Bit 7 of the status port controls the mask bit and reads the acknowledge flag.

#### READ STATUS

#### BIT 7 COMMENT

- 0 Acknowledge that data was received by the other interface. (Interrupt generated, if not masked.)

- 1 Data has been loaded into the output port.

#### WRITE STATUS

#### BIT 7 COMMENT

- 0 Mask out interrupt signal (Interrupt disabled on reset of IO5.)

- 1 Enable interrupt signal (INTR 5).

This output interface is set up to drive a Centronics-like printer. The sense line (sense 1) for the output is positioned to detect the busy line for the printer if it does not have an acknowledge signal.

The output interface (J5) is compatible with the input interface (J4); with two IO5s and two 26-conductor ribbon cables, a high speed data link can be set up between two S-100 computers (see Section 2.8 for application).

#### EXAMPLE SOFTWARE

Data in the C-Register is sent. Jumper E57 to E58 installed.

| ; PORT | ADDRESSES |            |

|--------|-----------|------------|

| KSTAT  | EQU       | 0CH        |

| KDATA  | EQU       | <b>ODH</b> |

;LOCATION OF EXAMPLE DRIVER LOC EQU 0E000H

ORG LOC

OPORT: IN KSTAT ;GET STATUS ANI 80H ;TEST DAK

| JNZ | OPORT |              |       |        |  |

|-----|-------|--------------|-------|--------|--|

| MOV | A,C   |              |       |        |  |

| OUT | KDATA | ; SEND DATA, | START | OUTSTB |  |

| IN  | KSTAT | ; END OUTSTB |       |        |  |

| RET |       |              |       |        |  |

## 2.6 TIMER

# 2.6.1 Jumper Options

The IO5 provides on-board three software programmable 16-bit interval timers. This part (8253) is set up so that one timer can be used as a master sub-interval timer (similar to 1 millisecond) and the other two timers as real-time clocks which can interrupt the main CPU. The on-board 1.8432 MHz oscillator or the 2 MHz bus clock signal can be used as the input to the interval timers. It is recommended that the 1.8432 MHz signal be used because the 2 MHz bus signal may not be available on some of the S-100 or IEEE 696 system configurations.

Each interval timer has an input, gate control, and output pin which is brought over to a strapping header (El thru El6).

| INPUT CLOCK Ø | EI | 0 | 0 | E9 PULL-UP TO + 5V |

|---------------|----|---|---|--------------------|

| GATE CTRL Ø   | E2 | 0 | 0 | EIO 2 MHz          |

| OUTPUT SIG Ø  | E3 | 0 | 0 | EII 1.8432 MHz     |

| INPUT CLOCK 1 | E4 | 0 | 0 | E12                |

| GATE CTRL 1   | E5 | 0 | 0 | E13                |

| OUTPUT SIG 1  | E6 | 0 | 0 | EI4                |

| INPUT CLOCK 2 | E7 | 0 | 0 | EIS OUTPUT SIG 2   |

| GROUND        | E8 | 0 | 0 | EIG GATE CTRL 2    |

|               |    |   |   |                    |

#### TIMER HEADER

Timer 0 is set up to be the sub-interval timer, while timers 1 and 2 can provide interrupts INTRO and INTRI for the system. Ell should be strapped to El in most cases.

## 2.6.2 Software Examples

Let us set up timer 0 for about a 1 millisecond sub-interval and timer 1 as a 50 or 60 Hz interrupting pulse.

a. Connect Ell to El on the strapping header.

- b. Connect E2 to E9.

- c. Connect E5 to E9.

- d. Connect E3 to E4.

The time-interrupt will be sent to INTRO on the INTERRUPT ORDER strapping header. The main time standard is 1.8432 MHz.

e. Set counter 0 to mode 3 which will make it a square wave generator.

f. Set counter 1 to mode 0 for an interrupt on a terminal count.

g. Set intervals:

# 50 MHz PULSE

60 Hz PULSE

Load CIRO with 2304 dec. Freq. = 800 Hz (1.25ms)Load CIRl with 16 dec. Interrupt = 50 Hz (20ms)

Load CIRO with 3072 dec. Freq. = 600 Hz (1.66 ms)Load CIR1 with 10 dec. Interrupt = 60Hz (16.66ms)

43 HI PRIDRITY

h. The computer system must restore the load number in counter 1 after each time-interrupt in:

Less than 1.25 msec

Less than 1.66 msec

or read the terminal count of counter and calculate a new load number. The 8253 continues to count down internally from FFFF Hex after one time period after the terminal count (0000 Hex) is reached.

EXAMPLE OF 50 Hz COUNTER SETUP (20 msec interval)

| : PORT | ADDRESSES |             |

|--------|-----------|-------------|

| CTR0   | EQU       | <b>08</b> H |

| CIRL   | EQU       | <b>09</b> H |

| CTR2   | EQU       | OAH         |

| MODE   | FOU       | OBH         |

| ;LOCATION | OF  | EXAMPLE         |

|-----------|-----|-----------------|

| LOC       | EOU | J <b>OE000H</b> |

|                                            |                                    |                                        |                                                                      | PRIDRITY                   |

|--------------------------------------------|------------------------------------|----------------------------------------|----------------------------------------------------------------------|----------------------------|

| ; PORT ADD<br>CIR0<br>CIR1<br>CIR2<br>MODE | RESSES<br>EQU<br>EQU<br>EQU<br>EQU | 08H<br>09H<br>0AH<br>0BH               |                                                                      | 35572 43 AI PRIOD 177      |

| ;LOCATION<br>LOC                           | of Exam<br>Equ                     | IPLE<br>OE000H                         |                                                                      | TO                         |

| ORG<br>JMP<br>JMP                          | LOC<br>INTZ<br>LOAD                |                                        |                                                                      | 12 30 10 DE<br>12 30 10 DE |

| INTZ :                                     | MVI<br>OUT<br>LXI<br>MOV<br>OUT    | A,36H<br>MODE<br>B,2304<br>A,C<br>CTR0 | ;CTR0, MODE 3, BINARY<br>;SET 1.25 MSEC CLOCK<br>;SET MSB OF COUNTER | (" + APD                   |

| FIXED:<br>LOAD:                            | LXI<br>MVI<br>OUT<br>MOV           | B,16<br>A,70H<br>MODE<br>A,C           | ;SET 20MSEC TIME<br>;CTR1, MODE 0, BINARY                            |                            |

|                                            | OUT<br>MOV<br>OUT<br>RET           | CTR1<br>A,B<br>CTR1                    | ;SET LSB OF COUNTER<br>;SET MSB OF COUNTER                           |                            |

112 Mary - MAIN (NT Re-enter at "FIXED" for another 20 millisecond time-out, or enter at "LOAD" with B and C registers set to a time of your choice.

#### 2.7 INTERRUPT CIRCUIT

#### 2.7.1 Introduction

If your applications are for a real-time multi-user or multi-tasking system, the flexibility of the IO5 interrupt circuitry should meet a wide variety of 8 and 16 bit CPU requirements for the IEEE 696 bus. The interrupt circuitry is set up to address three main areas of system integration:

ITES

- 1. Data is passed to the bus during an interrupt. The IO5 can pass a one byte instruction, one byte code or a one byte address during an interrupt acknowledge.

- 2. One of nine interrupt lines used. The IO5 can drive the main interrupt line or one of the 8 vector interrupt lines on the IEEE 696 bus.

# 3. Board arbitration for multiple interrupt cards.

The IO5 provides the ability to arbitrate by daisy chain, vector priority or address code during an interrupt acknowledge.

Item 1, on the passing of data, is important on what type of microprocessor is going to be used in the system. Some processors will accept a vector address byte, while others will have to poll (scan) the boards to find out who interrupted and then call a routine for service. The passing of one byte during an interrupt acknowledge for different processors can be listed as follows:

#### PROCESSOR INTERRUPT MODE

8080

Responds to a one byte instruction during an interrupt. The instruction is called a "restart instruction" and is a one byte call. The restart code vectors the 8080 to one of 8 address locations per the code.

| Mnemonic | Hex | Vectored | to Address |

|----------|-----|----------|------------|

| RST0     | C7  | 00       | Hex        |

| RST1     | CF  | 08       | Hex        |

| RST2     | D7  | 10       | Hex        |

| RST3     | DF  | 18       | Hex        |

| RST4     | E7  | 20       | Hex        |

| RST5     | EF  | 28       | Hex        |

| RST6     | F7  | 30       | Hex        |

| RST7     | FF  | 38       | Hex        |

|          |     |          |            |

**Z8**0

Responds in one of three ways:

Mode 0: The same as 8080.

**Z80** Mode 1: No code passed, the Z-80 vectors to address (con't.) 0038 Hex.

**Mode 2:** One byte is passed to form the least significant part of a 16-bit vector address. The most significant part of the address is stored in the I-Register. This 16-bit address points into a table where the address of the service routine must be stored.

All three modes of the Z80 are software programmable and are set to MODE 0 during a RESET. The most powerful mode is number 2, and it is supported by the IO5.

- 8085 Responds to a one byte instruction during an interrupt like the 8080. See 8080 processor interrupt mode.

- 8088/8086 Responds to a one byte identifier during an interrupt acknowledge. This one byte identifier is multiplied by 4 to give a table address at which the vector address to the service routine can be found. Identifiers of 20 Hex to FF Hex are allowed for external interrupts. This mode is easily supported by the IO5.

- 68000 Responds to a one byte table address during an interrupt acknowledge. The one byte table address is multiplied by 4 and expanded with additional zeros to give a 24-bit table address at which the address of the service routine can be found. The 68000 also puts out a priority code on address lines Al, A2 & A3 to signal which peripheral it will service during an interrupt acknowledge. The table byte can be 40 Hex to FF Hex for about 192 vector addresses. The IO5 supports Al thru A3 board arbitration as well as the one byte table address.

- **Z8000** Responds to a one byte jump vector during an interrupt acknowledge. The one byte jump vector is doubled, 30 is added to it, and then the program status area pointer is added to it. The new computed vector points to a table which has the address of the service routine. The one byte jump vector can be 00 Hex to FF Hex. The IO5 can pass one byte jump vectors during an interrupt acknowledge.

**Item 2,** on the selection of interrupt lines, will vary from system to system depending on the interrupt circuitry available on the CPU and other I/O boards. The most commonly supported interrupt line is INT (pin 73) on the IEEE 696 bus. The line NMI (non-maskable interrupt) is reserved for major errors within the system and power failure, so it was

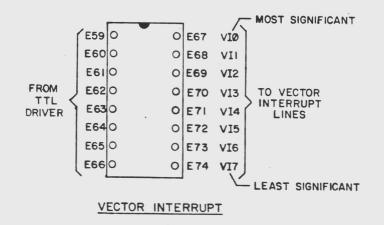

not considered as a jumper option on the IO5. The vector interrupt lines (VIO thru VI7) are mainly used with an interrupt controller circuit present on the CPU or external board. The IO5 can use the vector interrupt lines to arbitrate between multiple IO5s.

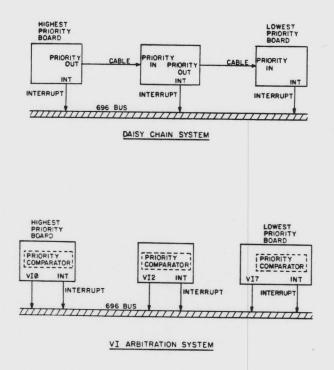

Item 3, on arbitration, will become a major issue when multiple interrupting boards are present on the bus. If no interrupt controller is present within the computer, the boards themselves must arbitrate. Two methods are available on the IO5:

- o "Daisy chain" cable connection between boards.

- o Arbitrate on the VI lines by priority.

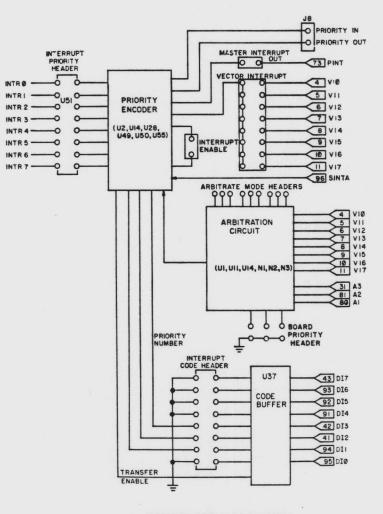

The IO5's interrupt circuit is divided into three sections: a priority encoder, an arbitration circuit, and a one byte code buffer. Refer to the Interrupt Circuit Block Diagram.

#### PRIORITY ENCODER

To control the order of transfer of the 8 on-board interrupting devices (serial, parallel and timer), a priority encoder circuit is utilized. The priority encoder receives the device interrupts through the INTER-RUPT PRIORITY HEADER so that the highest to lowest priority is userselectable. The output interrupt from the priority encoder is user strappable to the MAIN INTERRUPT or the VECTOR INTERRUPT lines of the IEEE 696 bus. The priority encoder has an INTERRUPT ENABLE jumper which must be strapped for interrupts to be passed to the CPU.

Two daisy chain signal pins have been provided to the priority encoder called PRIORITY IN and PRIORITY OUT, if daisy chaining is desired between boards.

#### ARBITRATION CIRCUIT

The arbitration circuit is used to prevent a bus conflict between multiple interrupting IEEE 696 boards. The arbitration circuit can be set up for one of three modes of operation:

- o Arbitrator disabled for daisy chain only operation.

- o Arbitrate by priority of the vector interrupt lines.

- o Arbitrate by priority number sent back by the CPU.

The arbitration circuit basically prevents the board from sending back an INTERRUPT CODE during an interrupt acknowledge from the CPU unless one of the three modes are met. The ARBITRATE MODE header and BOARD PRIORITY header sets the main arbitration mode.

#### CODE BUFFER

The one byte code buffer is used to pass an instruction or vector address byte to the CPU during an interrupt acknowledge. The code is user-selectable because it will depend on the capability of the microprocessor chip used. The INTERRUPT CODE header receives three lines from the priority encoder to pass the number of the on-board interrupting device wanting service. Only if the arbitrator's conditions are met will the code buffer be enabled to transfer data to the main CPU during an interrupt acknowledge cycle.

INTERRUPT CIRCUIT BLOCK DIAGRAM

As was indicated in Section 2.7.1 under item 1, a wide variety of microprocessors will accept a one byte code during an interrupt acknowledge cycle. The IO5 has an INTERRUPT CODE header which can provide a fixed code or a variable code, depending on its strapping.

#### INTERRUPT CODE HEADER

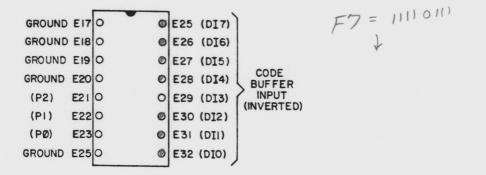

If pins E25 thru E32 are left unconnected, the data code will be 00 Hex during an interrupt acknowledge. If pins E25 thru E32 are connected to E17 (ground), the data code becomes an FF Hex.

The lines P0 thru P2 on the interrupt code header give a priority number of which on-board device is requesting service on the IO5. If the P0 thru P2 lines are mixed with ground connections to the data (DI) side of the interrupt code header, one byte instructions or vector addresses can be formed.

EXAMPLES 8080 (RESTART CODES) 625 E17 0 0 0 0 0 Ø 0 E32 E24 280 (MODE 2) E25 E17 -0 UPPER 4-BITS 0 USER DEFINED 0 PER BOARD 0 E32 E24 0 8086,68000,<del>2</del>8000 525 E17 0 00000 ALL BITS FOR 8086, CODE > IF HEX FOR 68000, CODE > 3F HEX USER DEFINED FOR 28000, CODE = OD to FF. Hex 0 0 E24 0 E3Z 0 Insert

:0

#### 2.7.3 CPU Interrupt Line

The IEEE 696 bus has 10 interrupt input lines. The IO5 can drive 9 of these interrupt lines. The line NMI (non-maskable interrupt) is reserved for major errors within the system and power failure, so it was not considered as a jumper option on the IO5.

## Interrupt Lines

| INT | (pin | 73) | VI2 | (pin | 6) | VI5 | (pin | 9)  |

|-----|------|-----|-----|------|----|-----|------|-----|

| VI0 | (pin | 4)  | VI3 | (pin | 7) | VI6 | (pin | 10) |

| VIl | (pin | 5)  | VI4 | (pin | 8) | VI7 | (pin | 11) |

The interrupt lines used by the IO5 can be strapped in several ways; the following are some examples:

- o One interrupt board only, no vector interrupt controller. Only INT needs to be driven, so jumper E51 to E52.

- Multiple interrupt boards, no vector interrupt controller, daisy chain protocol.

Only INT needs to be driven, so jumper E51 to E52.

- Multiple interrupt boards, no vector interrupt controller, VI arbitration.

Jumper E51 to E52 for INT. A different "VI" line is selected for each board by jumpering the VECTOR INTERRUPT header.

251-252

o Multiple interrupt boards, vector interrupt controller, VI arbitration. Leave E51 to E52 open A different "VI" line is select

Leave E51 to E52 open. A different "VI" line is selected for each board by jumpering the VECIOR INTERRUPT header.

The described interconnections are only examples, and therefore the user should not feel restricted to the few system configurations shown here:

29

# 2.7.4 Board Arbitration

# 2.7.4.1 Daisy Chain

To support an old scheme used by several S-100 manufacturers, a twopin daisy chain connector has been provided on the IO5. Daisychaining is a method (external from the IEEE 696 bus) of arbitrating between multiple boards equipped with interrupts by an inter-board cable. The highest priority board can send a signal to the next lowest priority board to disable his interrupt until the highest priority is serviced by the CPU. Boards are literally strung together by a cable from the highest priority one down to the lowest.

One major weakness to daisy chaining is the time it takes to propagate a disable signal down through all the boards on the interconnecting cable. During interrupt acknowledge time interval, part of the time is used for daisy chain propagation and part of the time for passing the interrupt data code to the CPU. If too may boards are daisy chained up, the CPU may not see the data code. The number of boards that can be daisy chained is governed by the CPU's speed and number of cycles allowed for an interrupt acknowledge.

The daisy chain connector has two pins, one pin for interrupt disable signal from a higher priority board, and the other pin to go to the next lowest priority board.

(TO LOWER OUTPUT PIN --INPUT PIN (FROM HIGHER DAISY CHAIN CONNECTOR , JG

If only daisy chaining is used for interrupt arbitration, the "VI" arbitration scheme must be defeated on the IO5 board in the following way:

- o No jumpers should be present on E81 thru E89 of the ARBITRATE MODE header.

- o Jumper E75 to E78

- o Jumper E76 to E79

- o Jumper E77 to E80

## 2.7.4.2 VI Lines

The VI (Vector Interrupt) lines can be used by multiple IO5 or IO8 interface boards for interrupt priority arbitration. This scheme is

faster than the daisy chain concept, so the number of interrupting boards does not affect performance of the system. In the VI arbitration scheme each of the I/O boards watches all 8 VI lines and only transfers interrupt data to the bus when that board's priority number is generated from an on-board priority encoder.

Each I/O board should be set up to drive **only one** VI line on the bus. The BOARD PRIORITY header should be set to match the number of that VI line. Up to eight I/O boards can use this arbitration scheme, and if each board was like the IO5, up to 64 serial interrupts can be prioritized and independently address vectored.

a. To enable this mode, first set the ARBITRATE MODE header as follows:

Jumper E82 to E83 Jumper E88 to E89 Jumper E85 to E86

- b. Next, set the priority of the board on the VECTOR INTERRUPT header by referring to the vector interrupt figure in Section 2.7.3.

- c. Set the BOARD PRIORITY header to match the vector interrupt line selected in Step 2.

| VI<br>SELECTED | E78<br>to<br>E75 | E79<br>to<br>E76 | <b>E80</b><br>to<br>E77 | PRIORITY<br>NUMBER | PRIORITY<br>LEVEL |

|----------------|------------------|------------------|-------------------------|--------------------|-------------------|

| 0              | no               | no               | no                      | 7                  | Highest           |

| 1              | no               | no               | yes                     | 6                  | •                 |

| 2              | no               | yes              | no                      | 5                  | •                 |

| 3              | no               | yes              | yes                     | 4                  | •                 |

| 4              | yes              | no               | no                      | 3                  | •                 |

| 5              | yes              | no               | yes                     | 2                  | •                 |

| 6              | yes              | yes              | no                      | 1                  | •                 |

| 7              | yes              | yes              | yes                     | 0                  | Lowest            |

#### 2.7.4.3 Address Lines

Presently, only the 68000 microprocessor is using this mode. The 68000 will send out on three of its address lines (Al,A2,A3) the priority level it will service during an interrupt acknowledge. Only the I/O board which matches this priority level can pass back a vector address byte.

a. To enable this mode, first set the ARBITRATE MODE header as follows:

Jumper E81 to E82 Jumper E87 to E88 Jumper E84 to E85 b. Next, set the priority of the board on the VECTOR INTERRUPT header by referring to the vector interrupt figure in Section 2.7.3. Be careful with your vector interrupt selection because restrictions may exist depending on the 68000 CPU board used.

| VI<br>SELECIED | E78<br>to<br>E75 | <b>E79</b><br>to<br><b>E76</b> | <b>E80</b><br>to<br>E77 | PRIORITY<br>NUMBER | PRIORITY<br>LEVEL |

|----------------|------------------|--------------------------------|-------------------------|--------------------|-------------------|

| 0              | no               | no                             | no                      | 7                  | Highest           |

| 1              | no               | no                             | yes                     | 6                  | •                 |

| 2              | no               | yes                            | no                      | 5                  | •                 |

| 3              | no               | yes                            | yes                     | 4                  | •                 |

| 4              | yes              | no                             | no                      | 3                  | •                 |

| 5              | yes              | no                             | yes                     | 2                  | •                 |

| 6              | yes              | yes                            | no                      | 1                  | •                 |

| 7              | yes              | yes                            | yes                     | 0                  | Lowest            |

#### 2.8 HIGH SPEED PARALLEL LINK

The parallel input (J4) and parallel output (J5) on the IO5 have been made signal and connector pin-compatible to allow the interconnection of two IO5's between two S-100 computers. Because both parallel interfaces have hardware handshaking capability, data can be transferred at a high speed with no baud rate restrictions except for the limitations of the CPU. A straight 26 conductor ribbon can be used to connect J5 to J4 or J4 to J5 between computers for one-way or two-way communications.

To input from J4, the sequence is (refer to Section 2.4):

To output from J5, the sequence would be (refer to Section 2.5):

32

This concept of a high-speed parallel link has been used successfully between two 696 computers running CP/M. Text files were PIPed across using the INP: and OUT: devices. The following assembly listing is what was used with PIP to allow the transfer:

|                                                                                                                 | ;Transfer routine for the IO5 to be used with PIP.<br>;Written by Malcolm T. Wright,11-5-81<br>;Last update 11-10-81. |                                          |                                                                                                                                                |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                 | ;file to creat                                                                                                        | e an IO5-PI<br>unications.               | overlayed on to a PIP.COM<br>IP.COM file for high speed<br>The new IO5-PIP.COM file uses                                                       |  |  |

|                                                                                                                 | ;>IO5-PIP OUT:                                                                                                        | =file.prn                                | To send data to the other CPU.                                                                                                                 |  |  |

|                                                                                                                 | ;<br>;>IO5-PIP newf                                                                                                   | ile.prn=INH                              | P: To receive data from the other CPU.                                                                                                         |  |  |

|                                                                                                                 | ;<br>;CONTROL-Z:<br>;<br>;                                                                                            | file an e<br>On an OUT                   | P: operation, a ctrl-z will close the<br>exit IO5-PIP.<br>F: operation, a ctrl-z will skip the<br>DAK for one character sent each time<br>ped. |  |  |

|                                                                                                                 |                                                                                                                       |                                          | ne in each computer system. The parallel<br>output (J5) ports are used.                                                                        |  |  |

| 000A =                                                                                                          |                                                                                                                       | Z80 or 8080                              | oth I/O routines to return in about 8<br>)) if communications is lost.<br>GREATER THAN 8.5 SEC AT 4MHZ                                         |  |  |

| 0080 =<br>^^9C =<br>3D =<br>0005 =<br>0001 =<br>000B =                                                          | KDATA EQU<br>BDOS EQU                                                                                                 | 80H<br>105 + 0CH<br>KSTAT+1<br>05H<br>01 | COMMAND ENTRY<br>SELECT CONSOLE IN<br>SELECT CONSOLE STATUS                                                                                    |  |  |

| 0109 =<br>001A =<br>010A =                                                                                      | PASS EQU<br>CTRLZ EQU<br>LOC EQU                                                                                      | 1AH g                                    | PASS DATA TO PIP<br>CONTROL-Z<br>Free space in PIP                                                                                             |  |  |

| 0103<br>0103 C30A01                                                                                             | ORG<br>JMP                                                                                                            | 103H<br>IPORT                            | PIP ENTRY FOR INPUT                                                                                                                            |  |  |

| 0106<br>0106 C34201                                                                                             | ORG<br>JMP                                                                                                            | 106H<br>OPORT                            | PIP ENTRY FOR OUTPUT                                                                                                                           |  |  |

| 010A                                                                                                            | ORG<br>;Input routine                                                                                                 |                                          | LOCATION OF ROUTINES                                                                                                                           |  |  |

| 010A E5<br>010B C5<br>010C 060A<br>010E 210000<br>0111 DB8C<br>0113 E601<br>0115 CA3B01<br>18 CD7301<br>011B B7 | IPORT: PUSH<br>PUSH<br>MVI<br>LXI<br>IP1: IN<br>ANI<br>JZ<br>CALL<br>ORA                                              | H,0<br>KSTAT<br>1<br>IP3                 | MULTIPLIER<br>SET TIMER<br>CHECK IO5 DAV<br>CHECK CONSOLE DAV                                                                                  |  |  |

| 011F<br>0122<br>0124<br>0126<br>29<br>-2A<br>012B<br>012C<br>012F | FE1A<br>CA3501<br>2B<br>7D<br>B4<br>C21101       | IPX:                | JZ<br>CALL<br>ANI<br>CPI<br>JZ<br>DCX<br>MOV<br>ORA<br>JNZ<br>DCR<br>JNZ |                                     | ;JMP IF NO DATA.<br>;GET CONSOLE DATA<br>;EXIT IF CTRL-Z<br>;DECREMENT TIMER<br>;WITHIN TIME?     |

|-------------------------------------------------------------------|--------------------------------------------------|---------------------|--------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------|

| 0133                                                              | 3E1A<br>320901<br>C1<br>E1                       | IP2:                | MVI<br>STA<br>POP<br>POP<br>RET                                          | A, CTRLZ                            | ;OUT OF TIME<br>;PASS DATA TO PIP                                                                 |

| 013D                                                              | DB8D<br>E67F<br>C33501                           | IP3:                | IN<br>ANI<br>JMP                                                         | KDATA<br>7FH<br>IP2                 | ;GET DATA<br>;REMOVE PARITY                                                                       |

|                                                                   |                                                  | ;Output             | routine.                                                                 | •                                   |                                                                                                   |

| 0142<br>0143<br>0145<br>0146<br>0147                              | D38D<br>E5<br>C5                                 | OPORT:              | MOV<br>OUT<br>PUSH<br>PUSH<br>MVI                                        | KDATA<br>H<br>B                     | ;GET 105 DATA<br>;SEND 105 DATA<br>;MULTIPLIER                                                    |

| 0149<br>014C<br>014E<br>50<br>0153                                | 210000<br>DB8C<br>E68U<br>CA7001<br>CD7301       | OP1:                | LXI<br>IN<br>ANI<br>JZ<br>CALL                                           | H,0<br>KSTAT<br>80H<br>OP2<br>CONST | ;SET TIMER<br>;CHECK IO5 DAK<br>;EXIT IF DAK SENSED                                               |

| 015A<br>015D<br>015F                                              | CA6401<br>CD7D01<br>E67F<br>FE1A<br>CA7001<br>2B | OPX:                | ORA<br>JZ<br>CALL<br>ANI<br>CPI<br>JZ<br>DCX<br>MOV                      |                                     | ;CHECK CONSOLE DAV<br>;JMP IF NO DATA<br>;GET CONSOLE DATA<br>;JMP IF CTRL-Z.<br>;DECREMENT TIMER |

| <br>0166<br>0167<br>016A                                          | B4<br>C24C01<br>05<br>C24C01                     |                     | ORA<br>JNZ<br>DCR<br>JNZ<br>MVI                                          | H<br>OP1<br>B<br>OP1                | ;WITHIN TIME?<br>;ERROR. NO DAK                                                                   |

| 0170<br>0171<br>0172                                              | Cl<br>El                                         | OP2:                | POP<br>POP<br>RET                                                        | В<br>Н                              |                                                                                                   |

|                                                                   |                                                  | -                   |                                                                          |                                     | onsole routines************************************                                               |

| 0177<br>7A<br>017B                                                | E5<br>0E0B<br>CD0500<br>E1<br>C1                 | ; Consolo<br>CONST: | CALL<br>POP<br>POP                                                       | B<br>H<br>C,CST<br>BDOS<br>H<br>B   |                                                                                                   |

| 017C                                                              | 69                                               | ;Consol             | RET<br>e input.                                                          |                                     |                                                                                                   |

|                                                                   |                                                  |                     |                                                                          |                                     |                                                                                                   |

| 017D | C5     | CONIN: | PUSH | В     |  |

|------|--------|--------|------|-------|--|

| 017E | E5     |        | PUSH | H     |  |

| 017F | 0E01   |        | MVI  | C,CIN |  |

| 0181 | CD0500 |        | CALL | BDOS  |  |

| 0184 | El     |        | POP  | H     |  |

| 95   | Cl     |        | POP  | В     |  |

| 36   | C9     |        | RET  |       |  |

|      |        |        |      |       |  |

|      |        |        |      |       |  |

0187

END

#### 2.9 STANDARD SETTIP

To simplify the use of the IO5 board, a few standard setup examples are listed. First, the jumpers and headers on the board relate to the following functions: 90-94 = 20 H

93-97

#### GENERAL.

E90 thru E97 . . . Set the board's I/O address. E56 thru E58 . . . Select Status/Data order. E53 thru E55 . . . Set timing of E-signal for U6. E98 thru E113 . . Baud rate selection. El thru El6 . . . Set up timer function.

#### INTERRUPTS

E33-E34, Interrupt Enable . . Must be jumpered if interrupts desired. E51-E52, Master Interrupt . . Drives PINT bus line. E59-E74, Interrupt Level . . Drives VIO thru VI7 bus lines. E81-E89, Arbitrate Mode . . . Select arbitration mode. E75-E80, Priority Number . . Board's priority number. E17-E32, Interrupt Code . . . Byte to be passed to the CPU. E35-E50, Interrupt Priority. Select which interface can interrupt.

#### 2.9.1 No Interrupts, no timer

#### CONNECT COMMENT

| <b>E9</b> 0 | thru E97  | Set board address per Section 2.1.1. |

|-------------|-----------|--------------------------------------|

| E57         | to E58    | Status/Data order selected.          |

| E54         | to E55    | Set timing for 8080 or Z80.          |

| E98         | thru Ell3 | Select baud rate per Section 2.2.1.  |

This setup is good for general purpose I/O operations where I/O status is polled and no timer or interrupts are desired.

## 2.9.2 Console Interrupt Only (8080 Mode)

This setup connects only one interrupt line for the console (serial-A, J1) on the INTERRUPT PRIORITY header. We will assume, as a simple example, that a 8080 or 8085 CPU will be used. The INTERRUPT CODE to be passed will be a RST 1 instruction (see Section 2.7.1). Only the PINT line (bus pin 73) will be driven, so daisy chaining must be used if more than one interrupting board is used in the computer.

#### CONNECT COMMENT E90 thru E97 Set board address per Section 2.1.1. E57 to E58 Status/Data order selected. E54 to E55 Set timing for 8080 or Z80. E98 thru E113 Select baud rate per Section 2.2.1. E33 to E34 Enable interrupt circuitry. E51 to E52 IO5 will drive PINT line. E75 to E78 Set up for daisy chain only.

| E76 to E79         | Set up for daisy chain only.                            |

|--------------------|---------------------------------------------------------|

| E77 to E80         | Set up for daisy chain only.                            |

| E41 to E43         | Interrupt from Serial-A (console) per<br>Section 2.2.5. |

| Set Interrupt Code | Set up a RST-1 instruction (CF Hex).                    |

| E17 to E25         | DI7=1                                                   |

| E25 to E26         | DI6=1                                                   |

| E27 & E28 open     | DI4 & DI5=0                                             |

| E29 to E30         | DI3=1                                                   |

| E30 to E31         | DI2=1                                                   |

| E31 to E32         | DI1=1                                                   |

| E32 to E24         | DI0=1                                                   |

# 2.9.3 Serial Interrupts (8080 Mode)

CONNECT

This setup will allow both Serial-A and Serial-B to interrupt. We will assume, as a simple example, that a 8080 or 8085 CPU is used. The INTERRUPT CODE passed to the CPU will be a RST-2 instruction (see Section 2.7.1) for Serial-B, and a RST-3 instruction for Serial-A. Only the PINT line (bus 73) will be driven, so daisy chaining must be used if more than one interrupting board is used in the computer.

| CONTRIDCT                                                                                                                                                    | COPPLEXI                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| E90 thru E97<br>E57 to E58<br>E54 to E55<br>E98 thru E113                                                                                                    | Set board address per Section 2.1.1<br>Status/Data order selected<br>Set timing for 8080 or 280<br>Select baud rate per Section 2.2.1 |

| E33 to E34<br>E51 to E52<br>E75 to E78<br>E76 to E79<br>E77 to E80<br>E41 to E49<br>E42 to E50<br>Set Interrupt Code<br>E17 to E25<br>E25 to E26<br>E27 open | Enable interrupt circuitry<br>IO5 will drive PINT line<br>Set up for daisy chain only<br>""""""""""""""""""""""""""""""""""""         |

| E27 open<br>E28 to E20                                                                                                                                       | DI3=0<br>DI4=1                                                                                                                        |