InterSystems Series II Z-80 Processor

for the S-100 Bus

User's Manual

Copyright 1979 by Ithaca InterSystems, Inc. InterSystems Publication 2000-1.0-U

#### InterSystems Series II

InterSystems Series II products present the first integrated computer system designed entirely to IEEE S-100 Standards. As such, it represents a powerful and versatile family of computers and accessories you can apply to virtually any computing task.

With Series II you have considerable flexibility in systems building, because the Series II architecture is modular and not tied to any particular type of computing. This modular and structural stability enables you to adapt your system easily to your changing computing needs.

As with all InterSystems Series II Products, the Series II Z-80 has been designed to take full advantage of the extensions and enhancements of the new IEEE S-100 bus specification, and yet remain compatible with the majority of pre-standard S-100 boards.

This owner's manual has been prepared to acquaint you with your processor and to serve as an aid in achieving its optimum use. Section 1 introduces the Series II Z-80 and provides some general information; Section 2 describes the use of the board in a system, how to use the memory management unit, vectored interrupt controller and other board features, and gives programming examples; Section 3 is a step-by-step guide to setup of the board for operation in your system, and the remaining sections provide technical details, parts list, and schematic diagram.

Your Series II processor has been fully tested and burned in at the InterSystems factory, and should work the first time in your system. If you have any problems with the unit in your system, give us a call at (607) 257-0190; our technical support personnel will be glad to assist you.

## EBRATA Edition 1, Z-80 ll Manuel May 19, 1980 -

The following material will be incorporated into Edition 2 of the Z-80 II Manual.

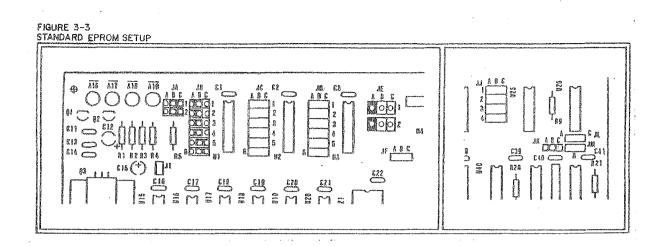

## EPROM Jumper Options

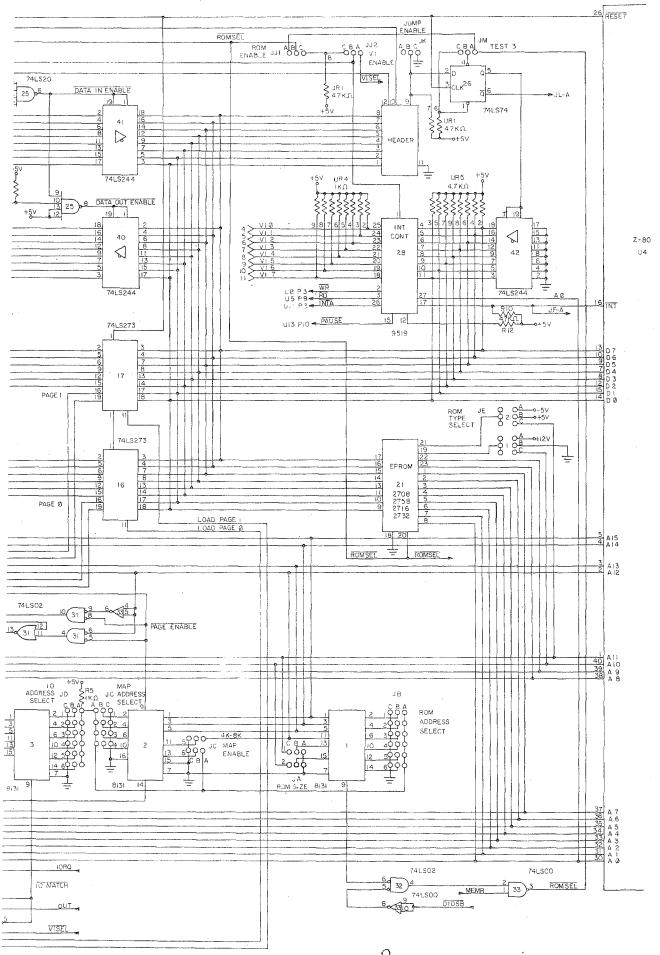

The chart at the top of page 46 is in error as regards the setting of the JA-1 and JA-2 Jumpers; the same chart is reproduced at the bottom of page 57 and is similarly in error. The standard setup table on page 55 has the same error. The chart on page 46 and page 57 should be as follows:

| TYPE   | JA-1    |          | JE - 5    | JB-6    |       | JE-2         |

|--------|---------|----------|-----------|---------|-------|--------------|

| 2708   | BC      | BC       | *         | *       | A     | ń            |

| 2758   | BC      | BC       | ж         | *       | В     | $\mathbf{F}$ |

| 2716   | BC      | AB       | *         | BC      | С     | $\mathbf{R}$ |

| 2732   | άB      | AB       | BC        | BC      | C;    | C            |

|        | (NO EPF | OM, JUMP | TO ANY 1  | K BOUN  | DARY) |              |

| NONE   | BC      | BC       | *         | ж       | С     | C            |

|        | (ST     | ANDARD = | 2708 AT F | :000 HE | X )   |              |

| STANDA | NRD BC  | ВC       | BC        | BC      | A     | ń            |

EPROM Type Select Jumpers

The settings of the JA-1 and JA-2 jumpers in the standard setup table on page 55 (under the "EPROM:" heading) should read:

1 K EPROM size

JA-1, JA-2 = BC

#### Nomencleture

The Z-80 II board is referred to as the ."mrU-80" board in most Intersystems' literature.

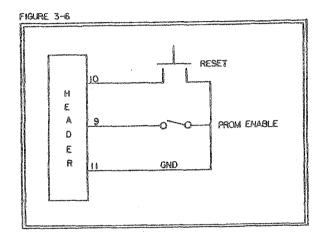

#### Header

The Z-80 II is designed to mate with a front panel via a 16or 20-pin DIP cable. The 20-pin DIP cable is not available in production quantities at this time, and in most current applications the 16-pin DIP cable is used. The socket provided on the Z-80 II card is, however, a 20-pin socket, providing for upward compatibility when 20-pin DIP cables become available. The 16-pin cable should be used in this socket RIGHT justified -- that is, holding the MFU-80 card with the S-100 connector pointing down, looking at the component side of the board, the 16-pin cable should so into the header socket so that it lines up with the right side of the header socket, and leaves four pin positions empty at the left side of the header socket.

In the case of the Intersystems front panel, the PIP cable will be properly aligned if no twist is introduced into it -- that is, if the right side of the UIP socket on the front panel is electrically connected to the right side of the DIP socket on the Z-80 II card. As regards other front panels, connect the DIP cable so that data bit zero goes to the right side of the DIP socket on the Z-80 II, data bit 1 goes to the next pin to the left, and so forth.

- 2 -

# TABLE OF CONTENTS

| 1.0 | Introdu                              | ction and General Information                                                                                                                                                                                                                                                                                                                                            | 1                                                              |

|-----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|     |                                      | stroducing the Series II Z-80<br>ervice Information<br>Receiving Inspection<br>Factory Service<br>Contacting InterSystems                                                                                                                                                                                                                                                | 2<br>3<br>3<br>4                                               |

| 2.0 | Series                               | II Z-80 Architecture                                                                                                                                                                                                                                                                                                                                                     | 5                                                              |

|     | 2.2 Ad<br>2.3 In<br>2.4 Z-<br>2.5 In | estem Design Overview<br>Noress Management for Large Systems<br>Memory Management Subroutines<br>Neterrupt Handling with the Series II Z-80<br>80 Processor Interrupt Modes<br>Mode 0<br>Mode 1<br>Mode 1<br>Mode 2<br>Neterrupt Controller Architecture<br>Neterrupt Controller                                                                                         | 6<br>7<br>12<br>16<br>18<br>18<br>19<br>19<br>20               |

|     | 0p<br>2.7 Cc<br>2.8 Us<br>2.9 Se     | Derating Options<br>Fixed or Rotating Priorities<br>Common and Individual Vectoring<br>Polled Mode<br>Master Mask<br>Status Register<br>Interrupt Service Register (ISR)<br>Information Transfers<br>Dommands to the Interrupt Controller<br>Sing the Interrupt Controller<br>eries II Bus Interface<br>.rect Memory Access Operations                                   | 21<br>22<br>22<br>23<br>24<br>24<br>24<br>24<br>28<br>36<br>37 |

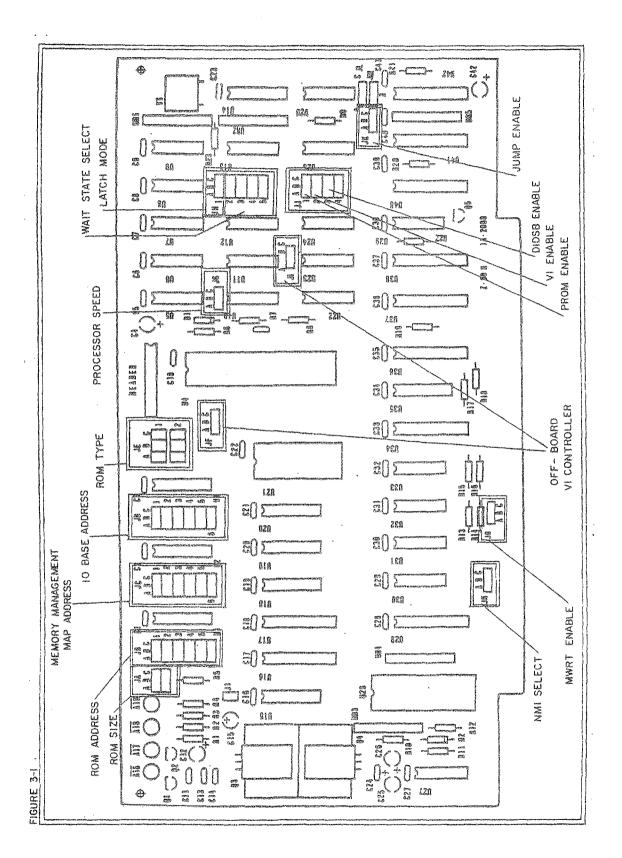

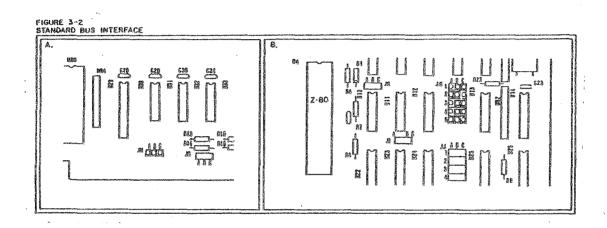

| 3.0 | Board S                              | Setup                                                                                                                                                                                                                                                                                                                                                                    | 39                                                             |

|     | 3.1 Bus                              | Interface Setup<br>Selecting the Processor Speed<br>Selecting the Latch Mode<br>Adding Single Wait States<br>Non-Maskable Interrupt Setup<br>The On-Board EPROM and Automatic Bootstrap<br>EPROM Type Selection<br>EPROM and Jump Address Selection<br>Enabling the EPROM and Jump<br>EPROM Wait States for 4 Mhz Operation<br>InterSystems Standard EPROM Configuration | 41<br>42<br>43<br>43<br>45<br>46<br>47<br>47<br>48             |

|     | 3.3  | Input/Output Port Setup                                       |          |

|-----|------|---------------------------------------------------------------|----------|

|     |      | I/O Base Address Selection                                    | 49       |

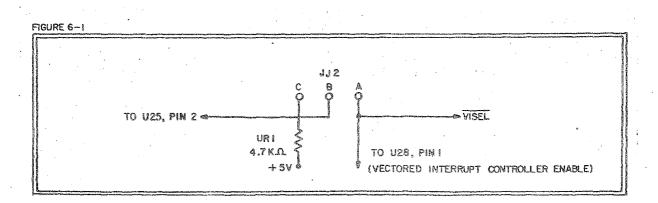

|     | 3.4  | Vectored Interrupt                                            | 50       |

|     |      | Controller Setup                                              |          |

|     | -    | Using an Off-Board Interrupt Controller                       | 50       |

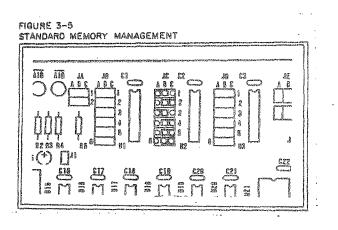

|     | 3.5  | Memory Management Setup                                       | 51       |

|     |      | Locating the Address Translator                               | 51       |

|     | ~    | Standard Memory Management Configuration                      | 52       |

|     | 3.6  | Front-Panelless Operation                                     | • 53     |

|     |      | Memory Write Strobe Generation<br>Front-Panel Control Strobes | 53<br>53 |

|     |      | The Header in Front Panelless Systems                         | 54<br>54 |

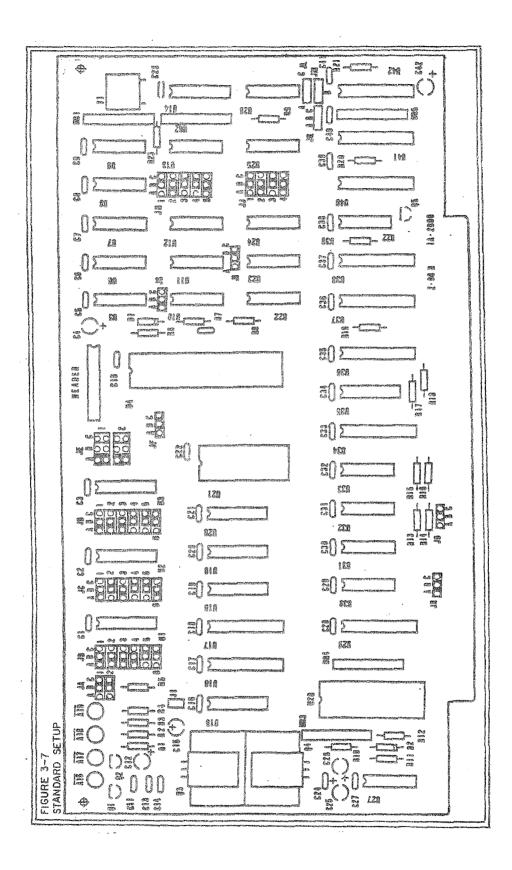

|     | 3.7  | Summary of the Standard Setup                                 | 55       |

|     | 3.8  |                                                               | 57       |

| •   | 3.9  |                                                               | 60       |

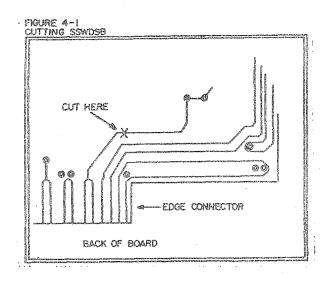

| 4.0 | Tech | nical Reference                                               | 61       |

|     |      | S-100 NDEF Lines                                              | 62       |

|     |      | Testing Modes                                                 | . 63     |

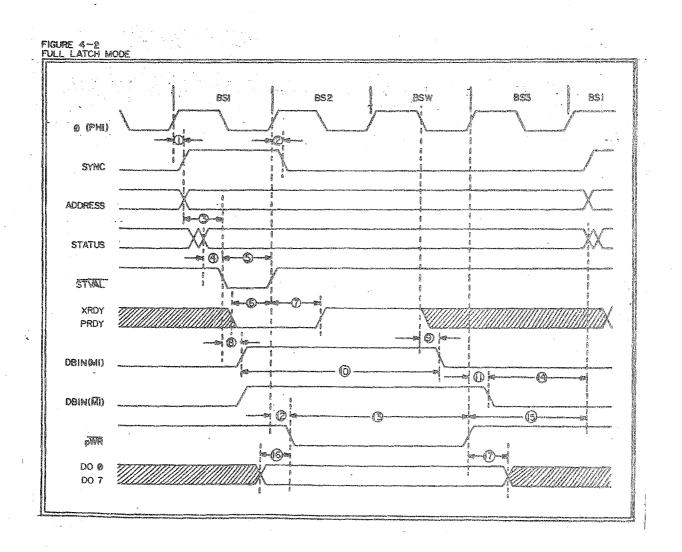

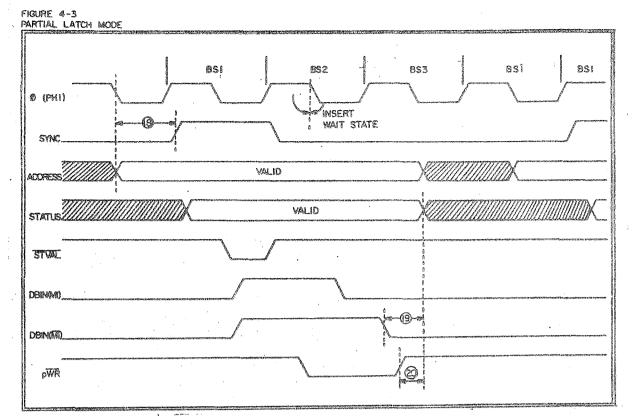

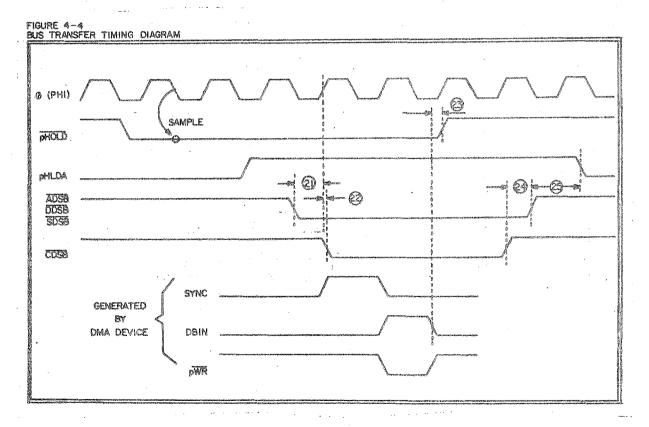

|     | 4.3  | Board Timing Diagrams                                         | 65       |

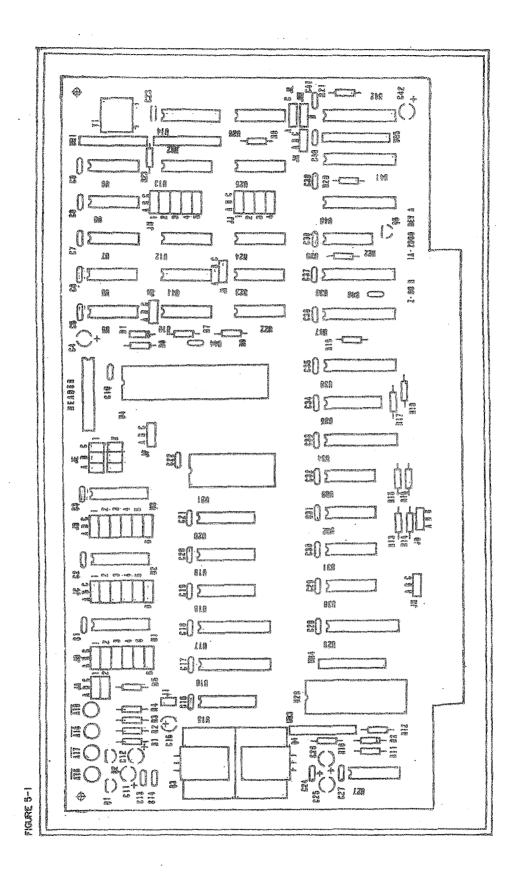

| 5.0 | Part | s List and Placement                                          | 69       |

| 6.0 | Revi | sions and Manual Applicability                                | 73       |

|     |      |                                                               | 1 1      |

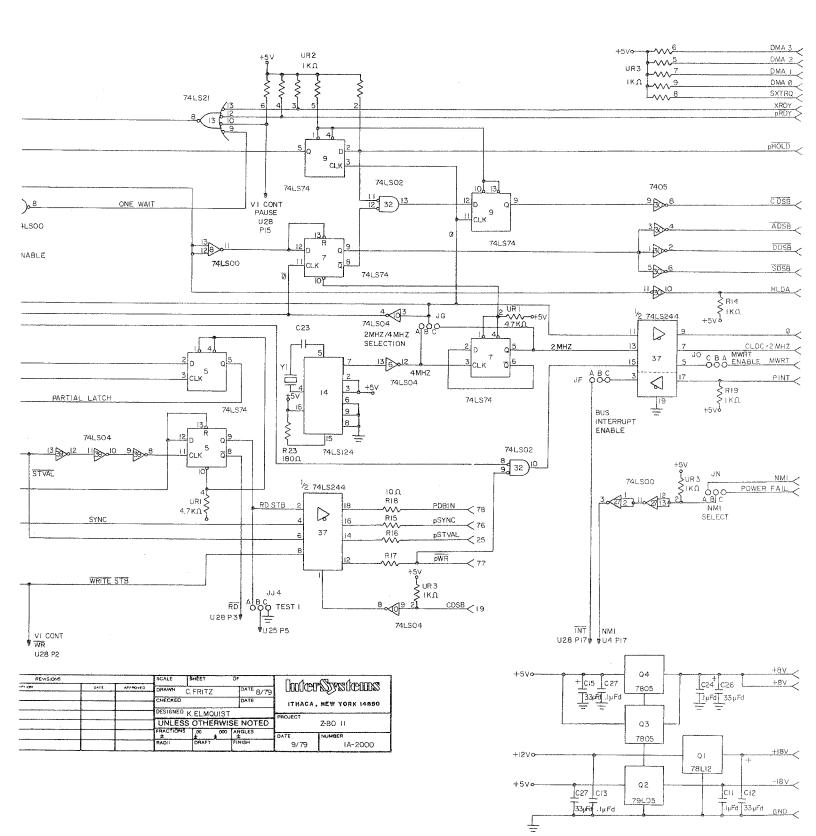

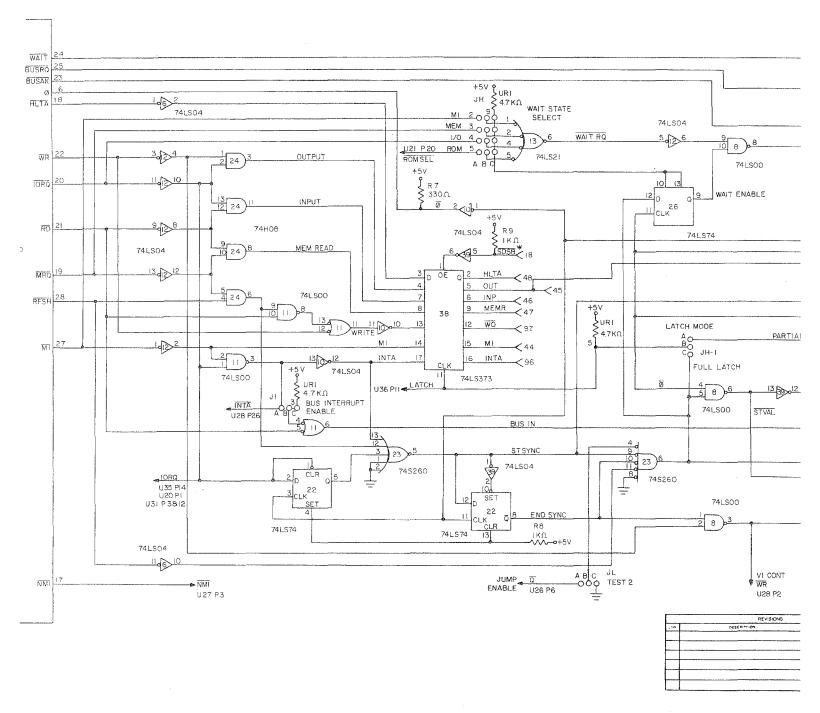

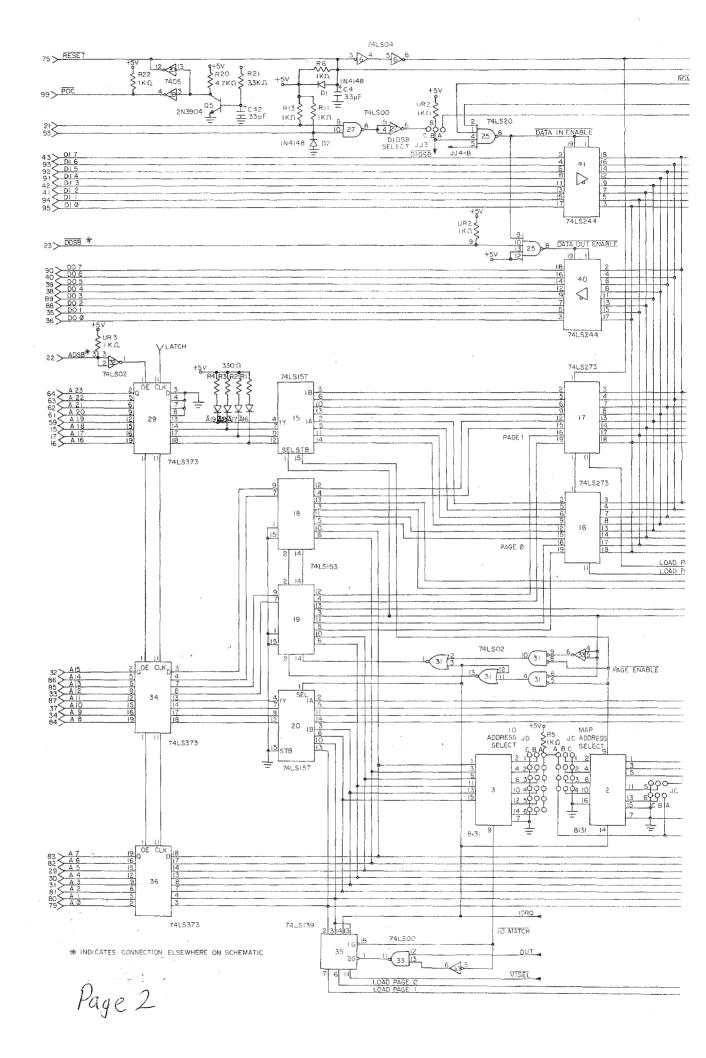

| 7.0 | Sche | matic Diagram                                                 | 75       |

|     | Itha | ca Intersystems Limited Warranty                              | 77       |

|     |      | ······································                        |          |

## Section 1

## Introduction and General Information

1.1 Introducing the Series II Z-80

1.2 Service Information

Receiving Inspection Replacement Parts Factory Service Contacting InterSystems

## 1.1 Introducing the InterSystems Series II Z-80

The InterSystems Series II Z-80 board is the first S-100 processor board to take full advantage of the recent IEEE specification. It has many special features that make it both powerful and easy to use. Among these features are:

- S-100 bus cycle generator creates IEEE standard bus cycle timing for all bus operations to guarantee compatibility with all IEEE S-100 products.

- 2) A simple address management system provides two 4 kilobyte segments relocatable anywhere in the first megabyte of the 16 megabytes of the S-100 address space. Four light-emitting-diodes indicate the four most-significant address bits.

- 3) Vectored Interrupt Controller gives sophisticated, high speed interrupt handling with individual masking, fixed or rotating priorities, and optional polled operation.

- 4) 2 or 4 mHz processor speed is on-board pin-jumper selectable.

- 5) PROM monitor socket will accept 2708, 2716, 2758, or 2732 EPROM's and a reset jump is provided to the PROM. The PROM may be addressed at any 1 K boundary in the 64 K address space.

- 6) On-board wait generator optionally adds a single wait state to any Instruction Fetch, Memory Reference, Input/Output Reference, or on-board PROM Reference.

- 7) On-board circuit conducts the IEEE specified nested bus transfer for glitch-free DMA operations, and DMA controllers need not duplicate the circuit.

- 8) Operation without a front panel is supported both by optional MWRT generation, and by a specially designed front-panel connector which includes the Reset, Jump Enable, and GND signals from the processor card.

- 9) Special engineering features include 2 self-test modes for quick circuit debugging and Address and Status latching to reduce bus noise and improve reliability.

#### 1.2 Service Information

Receiving Inspection

When your InterSystems Processor Module arrives, inspect both the equipment and the shipping carton immediately for evidence of damage during transit. If the shipping carton is damaged or water-stained, request the carrier's agent to be present when the carton is opened. If the carrier's agent is not present when the carton is opened, and the contents of the carton are damaged, save the carton and packing material for the agent's inspection. Shipping damages should be immediately reported to the carrier. Do not attempt to service the board yourself as this will void the warranty.

We advise that in any case you should save the shipping container for use in returning the module to InterSystems, should it become necessary to do.

#### Factory Service

InterSystems provides a factory repair service for all of its products. Before returning the module to InterSystems, first obtain a Return Authorization Number from our Sales Dept. This may be done by calling us, sending us a TWX, or by writing to us. After the return has been authorized, proceed as follows:

- 1) Write a letter describing the problem as best you can.

- 2) Describe your system to us, list boards by Manufacturer and name.

- 3) Include Xerox copies of the schematics of boards by manufacturers other than InterSystems.

- 4) Include the Return Authorization Number.

- 5) Pack the above information in a container suitable to the method of shipment.

- 6) Ship prepaid to InterSystems.

Your module will be repaired as soon as possible after receipt and return shipped to you prepaid.

## Contacting InterSystems:

The following apply both for correspondence and service.

Ithaca InterSystems Inc. 1650 Hanshaw Rd. P.O. Box 91 Ithaca N.Y. U.S.A. 14850

| Telephone | (607) | 257-0190 |

|-----------|-------|----------|

| TWX       | 510   | 255-4346 |

In Europe:

Ithaca InterSystems (U.K.) Ltd. 58 Crouch Hall Rd London N8 8HG. U.K.

Telephone Telex

- 4 -

01-341-2447 299568

## Section 2.0

Series II Z-80 Architecture

- 2.1 System Design Overview

- 2.2 Address Management for Large Systems Memory Management Subroutines

2.3 Interrupt Handling with the Series II Z-80

- 2.4 Z-80 Processor Interrupt Modes Mode 0 Mode 1

- Mode 2

2.5 Interrupt Controller Architecture

2.6 Interrupt Controller Operating Options Fixed or Rotating Priorities Common and Individual Vectoring Polled Mode Master Mask Status Register Interrupt Service Register Information Transfers

2.7 Commands to the Interrupt Controller

- 2.8 Using the Interrupt Controller Vectored Interrupt Controller Handlers

- 2.9 Series II Bus Interface

2.10 Direct Memory Access Operations

#### 2.0 Series II Z-80 Architecture

The Series II architecture supports a full range of system requirements, from small, dedicated applications to complex, multi-tasking systems. As a modular computing system, it is a flexible base from which to build a system tailored to your computing needs and achieve:

- Outstanding price/performance for all size systems.

- High standards of reliability and serviceability through the use of proven technologies, close adherence to the IEEE S-100 standard. and modular construction.

- \* Expandability to meet your future needs.

#### 2.1 System Design Overview

InterSystems Series II offers an integrated hardware and software system developed for the IEEE S-100 bus. At the core of the system are two compatible processors, the Series II Z-80 and the Series II Z-8000, offering the most sophisticated processing available for both 8 bit and 16 bit computer systems.

Memory requirements for both 8 and 16 bit compatible systems are handled by two new Series II memory boards, a 16 K static memory board and a 64 K dynamic memory board. Both these unique memories may be used in either 8 or 16 bit IEEE systems without modification and without wait states; the memory data bus automatically adjusts itself to the word width requested by the processor.

Series II Input/Output boards complete the hardware side of the system. Our multiple I/O board provides extremely versatile connection to all kinds of peripheral devices. The board provides 2 full RS-232 serial ports, 4 parallel ports, plus 8 bit addressable I/O lines for event sensing and control, and on-board interrupt prioritization.

Other Series II I/O boards include a high speed DMA floppy disk controller, capable of both single and double density; and an 8 bit, 8 channel Analog Input/Output board, as well as a forthcoming 12 bit analog I/O system. These sophisticated Input/Output systems are designed to contribute to the total efficiency of the Series II system, offering a flexible, modular approach for building your computing facility to meet your needs now and well into the future.

Software support for the Series II system revolves around our unique compiler, PASCAL/Z, available now for our 8-bit Z-80 system and available

soon for the 16 bit Z-8000 system. PASCAL/Z is rapidly becoming the industry standard for high speed, high efficiency Pascal programming.

Unlike most single card computer boards -- typically optimized for dedicated process control rather than for system support -- the Series II Z-80 offers a set of features that provide the core of a powerful general-purpose computer system. Instead of on-board random access memory, the Series II Z-80 provides segmented memory management. Instead of on-board Input/Output, the Series II provides Vectored Interrupt Control for the most efficient use of all system Input/Output. Instead of stripping down the S-100 bus interface to use the fewest parts, the Series II Z-80 cards are designed to produce the most reliable and consistent bus cycles.

#### 2.2 Address Management for Large Systems

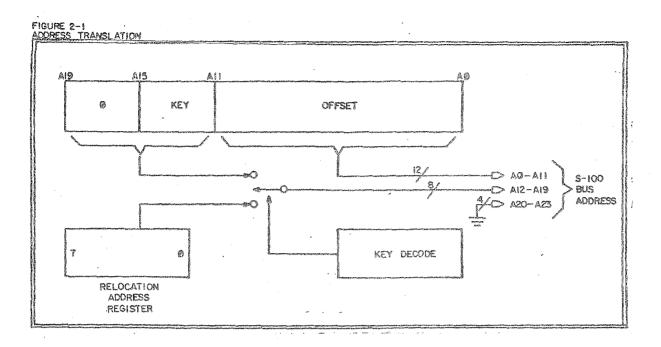

A dual segment address translator permits the Series II Z-80 to address memory beyond the 64 Kilobytes directly addressed by the processor chip itself. In this mode the Series II Z-80 card generates addresses that are 20 bits long, allowing access to any location in the first megabyte of the 16 megabyte S-100 address field. The extended address bits generated by the Series II Z-80, A16 throuh A19, are visually indicated by the four LED's in the upper left corner of the board. These lights indicate the complement of the address asserted on the bus, that is, a zero on the bus is indicated by a lighted LED. (The Series II Z-80 card always asserts the highest four address bits of the IEEE 24 bit extended address range -- A20 through A23 -- as zeros).

The address translator is configured as an 8 K "window" in the normal 64 K address space; the location of the window is set on the board with jumpers. When this window is addressed by the processor, the most significant four bits of the processor's address are replaced with a new four bits; in addition, four extended bits are also asserted. The remaining low address bits -- AO through A11 -- pass through the translator unchanged.

This new, extended address can access memory throughout a 1 Megabyte address space. The value of the "replacement" address -- the 8 most significant bits A12 to A19 -- is set dynamically on the card, by storing data in registers provided for this purpose. There are two such "relocation" registers, and the 8 K "window" is in fact split into two 4 K sections, so that two entirely different areas of the 1 Megabyte address space can be accessed conveniently. The address translation process is shown in Figure 2-1.

an l ar

Note that the area of main memory designated as the "window" is not lost to the processor: the relocation registers may be loaded such that the translated address is equal to the address generated by the processor before translation, thus providing "transparent" address mapping.

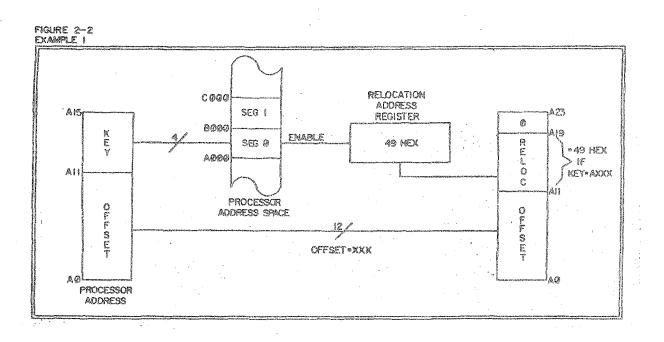

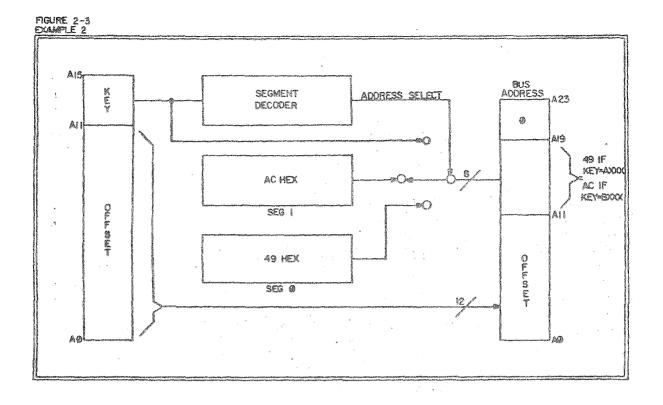

Some programming examples will help to illustrate the operation of the address translator. While the "window" area may be hardware addressed to any 8 K boundary, for the purpose of these examples we will assume that the 8 K window occupies the addresses from the 41st K to the 48th K (hex A000 to BFFF). This means that the first segment, SEG 0, is addressed from address A000 to AFFF, and the second segment, SEG 1, is addressed from B000 to BFFF (the card is shipped with the window addressed in this area).

As a first example, suppose we wish to move the first 2 K bytes of main storage (address 00,0000 to 00,07FF) to a block beginning in the extended storage area, say at address 04,9000 (hex). This may be easily done by loading the SEG 0 relocation register with the address 49 (hex) and transfering the data from locations 0 to 7FF to locations A000 to A7FF. The processor address "Axxx" ("x" is used to denote an arbitrary hex digit) selects the segment 0 translation. The top four bits of the processor's address ("A") are replaced by the contents of the relocation register, in this case 49 hex, and the low 12 bits of the processor's address are passed to the bus unchanged: The resulting bus address is 04,9xxx hex. See Figure 2-2.

As a second example, suppose we wish to move a 1 K block of data between two separate areas in the extended address space, say from 04,9000 to 0A,C000. If we load the SEG 0 relocation register with 49 and the SEG 1 register with AC, the transfer is accomplished by moving the contents of locations A000 thru A3FF to B000 thru B3FF. In this case the segment 0 designator (address Axxx) is replaced by address 49xxx, and the segment 1 designator (address Bxxx) is replaced by address ACxxx. (Figure 2-3)

Programs may also be run in the extended storage area. In this kind of operation the two segments may be grouped consecutively, giving a single 8K segment for the program. Programs should be assembled to run at address A000 and should be less than 8K bytes in length unless checking is done to assure that the program counter won't overflow back into main storage.

Even with these restrictions, this technique is extremely powerful for managing a set of overlays for a sophisticated program. All overlay programs may be assembled to run at address A000, but any number of overlays may be stored at random in the extended address space. Any of the stored overlays may be activated by loading the relocation registers with the appropriate pointers, and calling the overlay at address A000. Note that any location in the main storage area may be directly referenced by the current overlay, but that calls to other overlays should be routed through a kernel which will switch the requested overlay into the map area, and switch the first overlay back in on the return from the requested function.

The following programs are a simple set of subroutines which open either of the segments onto the specified areas of the system memory. Note that the routines do not limit the mappings to the extended storage area; any location in the first megabyte of memory may be accessed by these routines. For the purposes of simplicity, these subroutines will always consider the zero segment as an input file and the one segment as an output file, though there is no physical reason why both the segments may not simultaneously be input and output files.

The routines below initialize the memory management unit; open the input and the output files, get the next byte from the input file; put the next byte to the output file; check for window overflow and correct the relocation pointers if overflow occurs; and will move up to 64 K bytes from any location in memory to any other.

These simple routines could easily be combined with others to provide multiple open files, searching, sorting, overlay management, dynamic memory allocation, and a variety of other sophisticated system functions.

MEMORY MANAGEMENT SUBROUTINES \$ ŝ ;DEFINITIONS BASE ADDRESS OF ON-BOARD I/O IOBASE EQU OEOH IOBASE+2; ADDRESS OF RELOCATION REGISTER O EQU REGO IOBASE+3; ADDRESS OF RELOCATION REGISTER 1 REG1 EQU :RELOCATION POINTER FOR INITIALIZATION BASE EQU OAH ; SEGMENT O ADDRESSED AT A000 HEX KEYO EQU HOAO ; SEGMENT 1 ADDRESSED AT BOOO HEX 0 BOH KEY1 EQU ° 0 8 :ENTRY POINTS AND VARIABLES INIT: JMP INITO JMP **OPNINO** OPNIN: OPNOT: JMP OPNOTO GETB: JMP GETBO PUTB: JMP **PUTBO** MOVBLK: JMP MOVBKO ;INPUT VARIABLES INBASE DS 3 OTBASE DS 3 LEN DS 2 ;LOCAL VARIABLES SEGO DS Ś..... DS SEG1 1 INPTR DS 2 OTPTR DS 2 SEG DS 1 ; SUBROUTINE INIT: INITIALIZE THE MEMORY MANAGEMENT UNIT SUCH THAT THE SEGMENTS POINT TO THE SAME AREAS THEY PHYSICALLY ; OCCUPY IN THE MAIN MEMORY. IN THIS WAY THE RELOCATION DEVICE : IS LOGIALLY TRANSPARENT TO THE SYSTEM. USE A INITO: MVI A.BASE :LOAD A WITH BASE ADDRESS OF SEGMENT O OUT REGO ; SETUP SEGMENT O ; A=BASE ADDRESS OF SEGMENT 1 INR А OUT REG1 SETUP SEGMENT 1 RET ;EXIT

ŝ

```

;SUBROUTINE OPNIN: OPEN AN INPUT FILE IN THE EXTENDED ADDRESS

; AREA, BEGINNING AT THE ADDRESS GIVEN IN THE MEMORY LOCATIONS

;CALLED INBASE. SET THE SEGMENT O REGISTER WITH THE APPROPRIATE

:OFFSET AND SAVE AT SEGO. INPUTR IS THE POINTER TO THE FIRST

;BYTE OF THE INPUT FILE.

; USE A, F, D, E, H, L

;FORMAT OF INBASE IS INBASE=LEAST SINIFICANT BYTE, INBASE+1=

;MID-SIGNIFICANT BYTE, INBASE+3=MOST SIGNIFICANT BYTE (NOTE

;THAT BITS 4 THRU 7 OF THE MSB MUST BE 0'S)

00

OPNINO: LDED

INBASE ;LOAD DE WITH TWO LOW ORDER BYTES OF

; INBASE

LDA

INBASE+2:A=MSB OF INBASE

CALL

SPNT ; CALCULATE SEG AND OFFSET FROM A, D, E

STA

SEGO

SAVE SEGMENT POINTER AT SEGO

OUT

REGO

;SETUP THE SEGMENT REGISTER

MOV

A,H

ORI

KEYO

; INPNTR = A000+OFFSET

MOV

H, A

;SAVE AT INPNTR

SHLD

INPTR

RET

;EXIT

ŝ

ê

;SUBROUTINE OPNOT: OPEN AN OUTPUT FILE BEGINNING AT THE ADDRESS

CONTAINED AT OTBASE. SET THE SEGMENT 1 REGISTER WITH THE

; RELOCATION ADDRESS AND SAVE AT LOCATION SEG1. THE POINTER

;AT OTPTR IS THE OFFSET THAT POINTS TO THE FIRST BYTE OF THE

;OUTPUT FILE.

; USE A, F, D, E, H, L,

OPNOTO: LDED

OTBASE

LDA

OTBASE+2;LOAD A, D, E WITH ADDRESS IN OTBASE

CALL

SPNT ; CALCULATE RELOCATION AND OFFSET

STA

SEG1

;SAVE RELOCATION POINTER

OUT

REG1

;LOAD RELOCATION REG FOR SEGMENT 1

MOV

A,H

ORI

KEY1

;OFFSET+BOOO KEYS FOR SEGMENT 1

HOV

H,A

SHLD

OTPTR

; SAVE AT OTPTR

RET

EXIT

ŝ

```

;SUBROUTINE SPNT: CALCULATE THE RELOCATION POINTER AND THE ; OFFSET FOR LOADING TO THE MEMORY MANAGEMENT UNIT FROM THE ;20 BIT ADDRESS CONTAINED IN A,D,E (MSB TO LSB). ; RETURN THE RELOCATION POINTER IN A AND THE OFFSET IN HL. ;USE A, F, D, E, H, L SPNT: H, SEG ;HL POINT TO SEG LXI MOV :SEG GETS MID-BYTE OF BASE ADDRESS M.D RRD ; ROTATE DIGITS USING A AND SEG ANI OFH ;MASK BITS 4-7 OF OFFSET MOV H,A L,E MOV ;HL GET OFFSET LDA SEG ; A GETS RELOCATION POINTER RET ;EXIT 9 ; SUBROUTINE GETB: GET THE NEXT BYTE FROM THE INPUT FILE, ;AND INCREMENT THE INPUT POINTER, INPTR. CHECK FOR WINDOW ; OVERFLOW AND RECALCULATE THE OFFSET AND SEGMENT RELOCATION ; ADDRESS ON OVERFLOW. :USE A.F. HL. DE ; RETURN THE BYTE IN A. GETBO: ;HL POINT TO NEXT BYTE LHLD INPTR MOV BYTE IN D D.M INX Н ; INPNTR=INPNTR+1 MOV A,H CPI KEYO+10H; CHECK FOR SEGMENT OVERFLOW ;NO OVRFLW JNZ EXGET MVI H,KEYO ;OVRFLW, RESET INPNTR LDA SEG0 INR ;SEG0=SEG0+1 А STA SEG0 ; SAVE AT SEGO OUT REGO LOAD RELOCATION REGISTER WITH NEW VALUE EXGET: SHLD · INPTR ;SAVE POINTER TO NEXT BYTE MOV A,D ; RESULT IN A RET ;EXIT

ŝ

•

;SUBROUTINE PUTB: PUT THE BYTE IN A INTO THE OUTPUT FILE. ; INCREMENT THE OUTPUT FILE POINTER, OTPTR, AND CHECK FOR ;OVERFLOW. IF THE POINTER IS OUT OF THE 4K WINDOW, RECALCULATE ;THE RELOCATION POINTER AND THE OFFSET. USE A.H.L 2 PUTBO: ;HL POINT TO INSERT POSITION LHLD OTPTR MOV M,A STORE THE BYTE ;OTPTR=OTPTR+1 INX H MOV A,H CPI KEY1+10H ; OVERFLOW? JNZ EXPUT ;NO, GO ON MVI H.KEY1 RESET OFFSET ON OVRFLW SEG1 LDA INR A ;SEG1=SEG1+1 ON OVRFLW STA SEG1 ;SAVE NEW RELOCATION POINTER OUT REG1 :LOAD THE RELOCATION REGISTER EXPUT: SHLD OTPTR ; SAVE NEW OFFSET RET ;EXIT ;SUBROUTINE MOVELK: MOVE A BLOCK OF DATA OF THE LENGTH GIVEN IN :LEN FROM THE ADDRESS GIVEN IN INBASE TO THE ADDRESS GIVEN IN ;OTBASE. UP TO 64K BYTES MAY BE MOVED. ;USE A, F, B, C, D, E, H, L MOVBKO: CALL OPNIN ; OPEN THE INPUT FILE AT INBASE CALL OPNOT ; OPEN THE OUTPUT FILE AT OTBASE LBCD LEN ; BC GET LENGTH COUNTER MLP: CALL GETB GET THE NEXT BYTE CALL PUTB ;STORE THE BYTE IN THE OUTPUT FILE DCX В ;LEN=LEN-1 MOV A,C ORA В ;BC=0? JNZ MLP ;NO, GO ON RET ;YES, EXIT ŝ

SERIES II Z-80 CPU

## 2.3 Interrupt Handling with the Series II Z-80

All processor systems must transfer information to and from the user of the system, as well as process that information while it is in the system. Often computer systems have a number of peripheral devices connected to them, each with different requirements with regard to the frequency, urgency, and complexity of service needed from the system processor.

SERIES II Z-80 CPU

- 16 -

There are two general methods for coordinating these service requirements of assorted peripheral devices in a computer system: program controlled service routines, and interrupt driven service.

In a program controlled service system, the processor is responsible for the initiation and control of all peripheral device transfers, while in an interrupt driven system the peripherals themselves signal the processor that they require service. This signal, called an interrupt, modifies the sequence of instructions that the processor executes to include a service routine for the signaling peripheral.

As the number of system peripherals grows, or as the complexity of the service they require of the system increases, software polling techniques for coordinating device service become increasingly inefficient; the polling program becomes very time consuming, and quickly consumes a significant fraction of the processing resource. Even more disastrous to the overall efficiency of the system is that it becomes impossible to guarantee that a particular device will be serviced within a given amount of time, unless the attention of the processor is totally devoted to such a time critical-event.

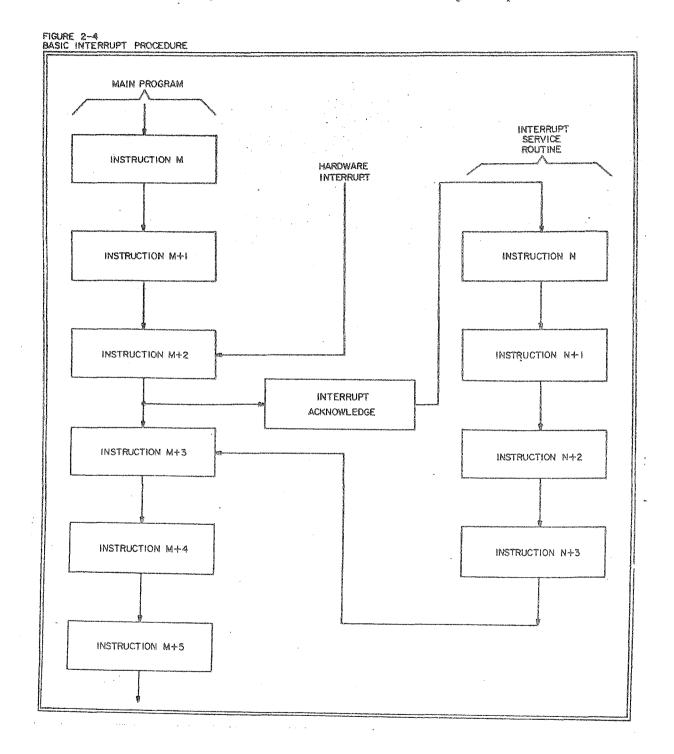

Interrupt driven systems, on the other hand, enhance the total throughput of the system by eliminating the need for software polling procedures, and have the additional advantage of priority resolution among simultaneous requests for processor service. A basic interrupt procedure is shown in Figure 2-4 (above). The instruction sequence of the main program is altered by the occurrence of a hardware interrupt at instruction M+2. The processor acknowledges the interrupt after the completion of the instruction, and branches to the interrupt service routine. When the interrupt service has been completed, the processor is free to return to the main program and continue execution.

The Series II Z-80 has been designed to support interrupt driven systems by the inclusion of a sophisticated vectored interrupt controller. The controller manages the masking of individual interrupts under software control, priority resolution among simultaneous service requests, and the vectoring for the 8 interrupt levels of the S-100 bus.

Additional features of the interrupt controller provide either a fixed priority mode for the resolution of multiple service requests, or a rotating mode such that all devices have, over time, equal priorities. The direct vectoring capability of the interrupt controller may also be bypassed and a polled mode option invoked under software control.

The integral mask register allows individual interrupts to be disabled or enabled by the processor. The mask register may be loaded either in parallel by the processor, or individual bits in the mask register may be controlled. The bus interrupt inputs to the controller use pulse-catching circuits to sense interrupt requests, so that both one-shot and stable requests will be accepted by the system. Narrow noise pulses, however, are ignored.

With this combination of features, interrupt systems of any complexity may easily be implemented. The following sections describe the internal architecture of the interrupt controller, its command structure, and provide a sample interrupt service handler.

#### 2.4 Z-80 Processor Interrupt Modes

The Z-80 processor chip has three basic modes of interrupt operation, which may be changed under software control. The Series II Interrupt Controller may be programmed to operate in any one of these modes; Mode 2, however, is by far the most powerful and versatile, and our programming examples will be confined to it.

#### Mode 0

Mode 0 is identical to the interrupt response mode of the 8080 processor chip. In this mode the interrupting device places an instruction on the processor's data bus during the Interrupt Acknowledge cycle. The processor then executes this instruction instead of the next instruction in memory. In theory any instruction may be placed on the data bus, but in practice only single byte instructions should be used because the Z-80 only produces an interrupt acknowledge cycle on the first byte of a multiple byte instruction. The single byte call instructions, called Restarts, are the instructions most often used in interrupt mode 0. These instructions execute a call to one of eight fixed locations in low memory, depending on the particular coding of the instruction. The interrupt controller may be programmed to supply any of the Restart instructions in response to any interrupt.

#### Mode 1

When interrupt mode 1 has been selected by the programmer, all interrupts in the system will be responded to by a call to location 066 Hex. A common service routine and dispatch table should begin at that location if mode 1 is selected.

Mode 2

Mode 2 is the most powerful interrupt response mode: a single byte response from the interrupt controller and an indirect call is made to any location in main memory.

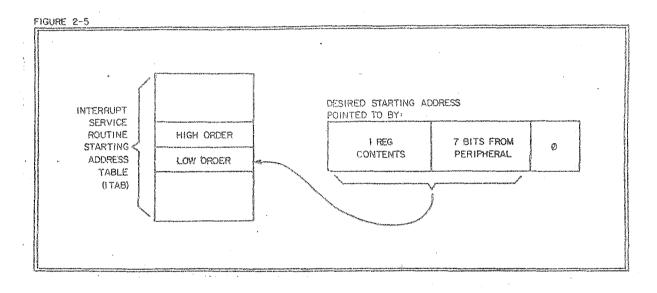

In mode 2, the programmer maintains a table of 16-bit starting addresses for all of the system's interrupt service routines. The table, called ITAB in the programming examples, may be located anywhere in memory, as long as it does not cross a 256 byte boundary. When an interrupt is accepted, a 16 bit pointer to the table is formed by the processor from the contents of a special register, the I register, which supplies the most significant 8 bits of the pointer, and the vector supplied by the interrupt controller during the acknowledge cycle, which supplies the least significant 8 bits of the pointer. The Z-80 then fetches the service routine starting address from the table entry selected by the pointer, and performs a call to the service routine.

Note that the address table, ITAB, must be located in memory such that the 16 bit service addresses always start on even addresses, and that the least significant bit from the interrupt controller is always a 0. Figure 2-5 illustrates the operation of mode 2 interrupts.

## 2.5 Interrupt Controller Architecture

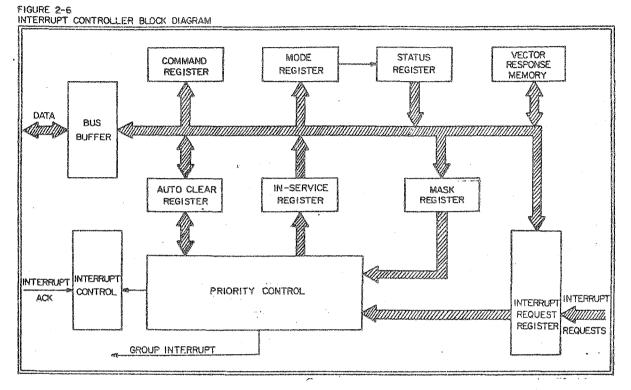

Figure 2-6 gives a block diagram of the interrupt controller used on the Series II Z-80. Interrupt requests are captured by the interrupt request register (IRR) where noise spikes are filtered out and the interrupt requests are latched. Any requests that are not masked by the interrupt mask register (IMR) are passed to the priority control circuitry where they will cause a group interrupt to be generated. When the processor accepts the interrupt, it issues an interrupt acknowledge signal which causes (1) the priority of all pending interrupt requests to be resolved, and (2) the byte from the vector response memory associated with the highest priority request to be asserted on the processor's data bus. The Z-80 processor uses this response vector as a pointer to a table of service routine addresses, fetches the appropriate address from the table, and executes a subroutine call to that address.

Other interrupt management functions are controlled by the Auto Clear register, the interrupt service register, and the mode register. All setup and programming of the interrupt controller is exercised through the command register, and the internal state of the controller is available in the status register.

## 2.6 Interrupt Controller Operating Options

. .

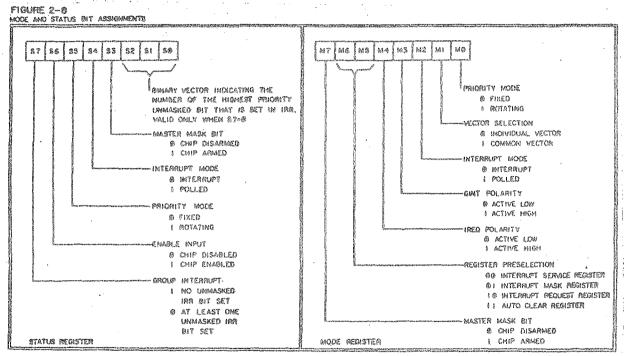

The interrupt controller's mode register is used to establish the basic operating conditions and options for constructing an interrupt driven system.

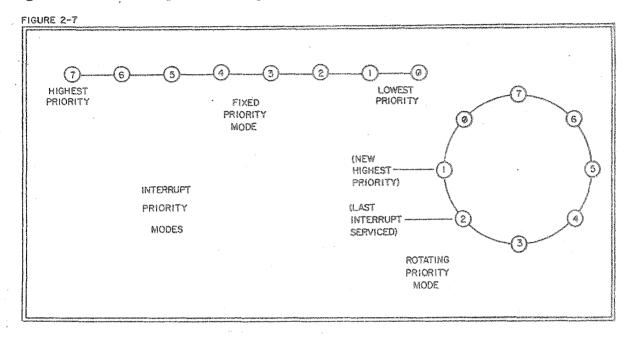

#### Fixed or Rotating Priorities

Bit MO in the mode register specifies whether the interrupt controller operates in the fixed priority mode or in the rotating priority mode. The fixed priority mode (MO=0) assigns the eight interrupt request inputs the priority they are assigned on the S-100 bus, that is, the VI 7 line is the highest priority interrupt in the system and the VI 0 line is the least significant interrupt in the system. This is shown in Figure 2-7.

The fixed priority mode is the one most often used, although there exists a possibility that low priority interrupts may never be serviced in a heavily loaded system. The individual masking feature, however, may be used to modify the effective priority structure of the interrupt controller to guarantee service to all peripherals.

In the fixed priority mode interrupts are normally masked such that only an interrupt of a priority higher than the interrupt being serviced may generate a new group interrupt to the processor. With the Series II Z-80, each interrupt may be specified to erect such a masking "fence" or not to, by setting the corresponding bit in the Auto Clear register, allowing a great deal of flexibility in the effective system priorities of each interrupting device.

If the eight interrupts have similar priority and bandwidth requirements, one effective solution is to select the rotating priority option (MO=1). As shown in the figure, the relative priorities in the system remain the same, except that the chain is closed into a circle. In rotating priority mode, however, the lowest priority position is assigned by hardware to the last interrupt serviced. This rotating priority scheme prevents any single interrupt from dominating the system. It assures that any interrupt will

not have to wait more than seven interrupt cycles before being serviced. Note that there is no nesting of interrupts in the rotating mode; all pending interrupts are masked from the processor while an interrupt is being serviced.

### Common and Individual Vectoring

Bit M1 in the mode register specifies whether the individual interrupts will branch to different locations upon acceptance of an interrupt, or whether all interrupts will branch to the same location. In the common vectoring mode, the response associated with IREQO (VI 7) will be asserted upon which interrupt is being regardless oſ interrupt acknowledge. The common vectoring mode is useful if all service routines acknowledged. save the total machine state before entering the actual device service In such a case, the processor branches to the common register save routine. routine, then polls the interrupt controller to discover the highest priority interrupt pending, and branches to the appropriate service procedure. This approach avoids duplication of the register save routine. Bit M1=0 selects the individual vectoring mode while M1=1 selects common vectoring.

### Polled Mode

Bit 2 of the mode register allows the system to disable the group interrupt output from the interrupt controller. In the polled mode the processor may read the status register in the interrupt controller to see if any interrupt requests are pending, and which request has the highest priority. Interrupt request bits may be cleared by software. The polled mode option then bypasses the hardware interrupt, the vectoring and fencing functions of the interrupt controller while the request latching, masking, and priority resolution remain unaffected. Bit M2=0 selects the interrupt mode, M2=1 selects the polled mode.

#### Master Mask

Bit 7 of the mode register specifies the status of the master mask bit of the interrupt controller. When the master mask bit is set, (M7=0) the controller is disarmed just as if all the mask bits in the mask register had been set. When bit 7 is a 1, the chip is armed and any unmasked active requests will cause an interrupt output.

The remaining bits of the mode register specify (1) the polarity of the group interrupt output, which is always active low on the Series II Z-80 (M3=0); (2) the polarity of the interrupt request signals, which is always active low in S-100 systems (M4=0); and (3) the register pre-selection address. These bits select which of the internal registers will be read by

the processor during a data read operation from the controller. A summary of the data transfer to and from the controller is given in a later section.

### Status Register

The Status register describes the internal state of the interrupt controller, as summarized in Figure 2-8. The 8 bits of the status register reflect the operating modes described above, and indicate the highest priority unmasked interrupt that is pending. Status bits SO-S2 contain the complement of the binary vector indicating the highest priority interrupt pending. The field should be considered invalid unless the status bit S7 (the group interrupt bit) is set (S7=1), indicating that at least one of the interrupt request bits is set and unmasked. Status bit S3 indicates the condition of the master mask in the Mode register. S3 equals 0 indicates that the chip is disarmed, S3 equals 1 indicates the chip is armed. Bit S4 indicates whether the controller is in interrupt mode or polled mode, and bit S5 indicates whether the priority resolution is in fixed or rotating mode. Finally, bit S6 is not used in this implementation.

The Status register is read directly by executing a read from the controller's control port; it does not require any preselection.

#### Interrupt Service Register (ISR)

The ISR is eight bits long and is used to store the acknowledge status of the interrupt requests. When an interrupt is acknowledged, the controller clears the associated request bit and sets the corresponding bit in the ISR. When the ISR bit is programmed for automatic clearing, the ISR bit will be cleared before the end of the acknowledge sequence. If it is not set for auto-clear, the ISR bit must be cleared by command from the Z-80.

Internally, the controller uses the ISR to erect a "masking fence". When an ISR bit is set and the fixed priority mode is selected, only an interrupt of higher priority than the one being serviced will cause a new interrupt output, nesting the interrupt routines, and moving the masking fence up to the new level. New interrupt requests of a priority lower than the one being serviced will be masked until the ISR is cleared by the Z-80. When the Auto Clear is specified, no masking fence is erected, since the ISR bit is cleared during the acknowledge sequence. The Auto-Clear function may be specified for each interrupt individually, by setting the associated bit in the Auto Clear register (ACR).

## Information Transfers

There are two input/output ports associated with the interrupt controller -a control port and a data port. A read operation executed from the control port will always read the status register, and a write to the control port will always write into the command register. When a read or write is executed to the data port, however, the information transfered depends on which of the internal registers has been pre-selected by the preceding command. During read operations, the Interrupt Request Register (IRR), the Interrupt Service Register (ISR), the Interrupt Mask Register (IMR), or the Auto Clear Register (ACR) are pre-selected for reading by the bits M5 and M6 of the mode Register. For writing into these registers, specific commands must be issued to the controller; the M5 and M6 bits do not preselect registers for writing.

#### 2.7 Commands to the Interrupt Controller

The interrupt controller's command set allows the Z-80 processor to select and alter all the operating modes described above, to customize the controller for different applications. Commands are entered into the command register by writing to the control port. In the commands described below, "X" indicates a "don't care" bit position. RESET

## Coding: 0000000

The reset command establishes a known internal condition in the interrupt controller:

Mode = Fixed priority, individual vectors, interrupt (non-polled) operation, interrupt inputs and output in the active low sense (normal), ISR preselected for reading, chip disarmed by master mask.

IMR = all ones, all requests are masked. ACR = all zeros, no auto clear specified. ISR and IRR are cleared of all old requests.

CLEAR IRR AND IMR

Coding: 00010XXX

All bits in the Interrupt Request Register and the Mask Register are cleared, no interrupts pending, no interrupts masked.

CLEAR SINGLE IMR AND IRR BIT Coding: 0 0 0 1 1 B2 B1 B0

A single bit is cleared in the IMR and the IRR. The bit is specified by the three bit field B2-B0 where:

| B2                           | B1 | BO                                        | BIT SPECIFIED                                                                 |  |

|------------------------------|----|-------------------------------------------|-------------------------------------------------------------------------------|--|

| Paris Conto Paris Cons Alter |    | - 1110 AUN 1723 1993 VIII ANN 4825 (188 A | 17 2256 2275 1769 2869 4866 6866 6276 4286 6276 6276 6270 6865 6866 6866 6866 |  |

| 0                            | 0  | 0                                         | 0 (LSB)                                                                       |  |

| 0                            | 0  | 1                                         | 1                                                                             |  |

| 0                            | 1  | 0                                         | 2                                                                             |  |

| 0                            | 1  | 1                                         | 3                                                                             |  |

| 1                            | 0  | 0                                         | 4                                                                             |  |

| 1                            | 0  | Peri                                      | 5                                                                             |  |

| 1                            | 1  | . 0                                       | 6                                                                             |  |

| 1                            | 1  | ţ.                                        | 7 (MSB)                                                                       |  |

|                              |    |                                           |                                                                               |  |

CLEAR IMR

.

Coding: 00100XXX

All bits in the IMR are cleared to zeros, thus all interrupt requests are unmasked.

CLEAR SINGLE IMR BIT

### Coding: 0 0 1 0 1 B2 B1 B0

A single bit in the mask register is cleared, as specified in the field B2-B0.

SET IMR

Coding: 00110XXX

All bits in the mask register are set to ones, thus masking all interrupt requests.

SET SINGLE IMR BIT Coding: 0 0 1 1 1 B2 B1 B0

A single mask bit is set, corresponding to the bit specified in the three bit field. The corresponding interrupt is then masked out of the priority resolution circuitry.

CLEAR IRR Coding: 01000XXX

All bits in the request register are cleared to zeros. New transitions on the interrupt inputs will be necessary to cause an interrupt.

CLEAR SINGLE IRR BIT Coding: 0 1 0 0 1 B2 B1 B0

A single request bit is cleared to zero, specified by B2-B0.

SET IRR

Coding: 01010XXX

All the request bits are set to ones, any unmasked bit will cause an interrupt output. Useful in testing.

SET SINGLE IRR BIT

Coding: 0 1 0 1 1 B2 B1 B0

A single request bit is set, corresponding to the bit specified by B2-B0.

CLEAR ISR

Coding: 01110XXX

All Service register bits are cleared to zero, fencing is eliminated.

- 26 - -

CLEAR HIGHEST PRIORITY ISR BIT Coding: 0110XXXX

The highest priority bit in the service register is cleared. Caution should be exercised in using this command if the auto clear option is specified, since the bit cleared by this command may not be the bit intended.

CLEAR SINGLE ISR BIT Coding: 0 1 1 1 1 B2 B1 B0

The bit specified by B2-B0 is cleared in the service register.

LOAD MODE BITS MO THROUGH M4 Coding: 1 0 0 M4 M3 M2 M1 M0

The five low order bits of the mode register are loaded. This command controls all operating options except the Master Mask and read preselection.

CONTROL MODE BITS M5,M6,M7 Coding: 1 0 1 0 M6 M5 N1 N0

The field in the command is loaded into the register preselect bits in the mode register. The N1, NO field in the command controls the master mask as follows:

| N 1                                                                                                                        | NO                                   |                                                                                                            |  |  |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| 1873) 490m (1976) (1976) (1977)                                                                                            | u 1950 (90) Şilə Qan taar taa 1969 u | න්ට ප්රාස ලංකා පාලල දිනාව වෙනය නොක නිමාල ගිවන පුලුලා ගිරින ප්රාන් ප්රාන් කොක නියාන නිමානි තිබර් නියාන නිමා |  |  |

| 0                                                                                                                          | 0                                    | NO CHANGE TO M7                                                                                            |  |  |

| 0                                                                                                                          | 1                                    | SET M7                                                                                                     |  |  |

| 1                                                                                                                          | 0                                    | CLEAR M7                                                                                                   |  |  |

| 1                                                                                                                          | . 1                                  | (illegal)                                                                                                  |  |  |

| რის სათ მოყ მის წილ დაგ მია რია დაგ მია რია თა თა მია მია მია მია ქია მაა ყა მია თა ქია თა და და და თა იდა მია მია მია მია |                                      |                                                                                                            |  |  |

PRESELECT IMR FOR WRITE Coding: 1011XXXX

The next write to the controller's data port will load the mask register. Various read operations may be inserted between this command and the write operation.

PRESELECT ACR FOR WRITE Coding: 1 1 0 0 X X X X

The auto clear register will be loaded on the next write to the data port.

## PRESELECT RESPONSE MEMORY FOR WRITE Coding: 1 1 1 0 0 L2 L1 L0

The vector response memory is preselected for writing, the byte which will serve as a pointer to the Z-80's service jump table will be loaded on the next write to the data port into the level specified by L2-L0 where:

| L2                                                                                                              | L1                      | LO                                                                                                              | BUS INTERRUPT (VI #)                                                                                         |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| 100 cm cr m m                                                                                                   | an an an sa sa sa sa an | 1 1000 Aline pres Aline and anno 1000 ann | n and and ally and ally and the set of an and set of an and set of an and set of an and an and an and an and |  |

| 1                                                                                                               | 1                       | 0                                                                                                               | VI 1                                                                                                         |  |

| 1                                                                                                               | 0                       | 1                                                                                                               | VI 2                                                                                                         |  |

| 1                                                                                                               | 0                       | 0                                                                                                               | VI 3                                                                                                         |  |

| 0                                                                                                               | 1                       | 1                                                                                                               | VI 4                                                                                                         |  |

| 0                                                                                                               | 1                       | 0 .                                                                                                             | VI 5                                                                                                         |  |

| 0                                                                                                               | 0                       | 1                                                                                                               | VI 6                                                                                                         |  |

| 0                                                                                                               | 0                       | 0                                                                                                               | VI 7                                                                                                         |  |

| eau ben dat alle uit den lier van ein ein eus een een een een een een een een dat een dat een war een aan de be |                         |                                                                                                                 |                                                                                                              |  |

### 2.8 Using the Interrupt Controller

Before the Interrupt Controller can do useful work it must be initialized under control of the Z-80 processor. Because of the many operating options available with the interrupt controller, the controller may be programmed using many different approaches. The following is but one of these ways to construct a basic initialization and service routine.

- 1) Disable Processor interrupts

- 2) Reset the interrupt controller

- 3) Setup vector response memory

- 4) Load operating options into the mode register

- 5) Load the mask conditions into the IMR

- 6) Clear the IRR

- 7) Clear the master mask

- 8) Set processor interrupt mode to mode 2, and load the service jump table.

- 9) Enable interrupts.

The following simple program uses the Z-80 interrupt mode 2, and is intended to both serve as a test of the interrupt controller and an example program for using the interrupt controller.

| 8<br>8<br>9                       | D tonk of the one of the              |                        | IPT CONTROLLER HANDLERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|---------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; SUPPOR<br>; INTERR              | t to set<br>upts on (                 | UP AND RI<br>THE S-100 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   |                                       |                        | TH INTERRUPT DRIVEN AND POLLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| v                                 |                                       |                        | DTATING PRIORITIES, ARBITRARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                   |                                       | KING, ANI              | ARBITRARY AUTO-CLEAR FOR NESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ;CONTRO                           | Le n                                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                                 | June 1999 1999 1999 1999 1999 1999 19 | 1990                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ;SAVED                            |                                       | RY TO AN               | IN REGISTER BANK OF THE Z-80 CPU ARE<br>INTERRUPT PROCEDURE, AND RESTORED<br>IRRUPT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |