# OMNI256 Board 256k Static Ram for IEEE-696/S-100

Technical Reference Manual

August 1985

Copyright (C) 1985 by Fulcrum Computer Products

All rights reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, without the prior written permission of Fulcrum Computer Products.

DISCLAIMER

This manual contains information which is subject to change without notice. Fulcrum Computer assumes no responsibility for any errors which may be contained within this manual.

## OMNI256 Board Technical Reference Manual

# Table of Contents

| 1. | INTRO                                    | DDUCTIO                                                        | N                             |                   |                         |            |     |          | * 1 |   |     |        | * * |     |     |     | *   | <br>* | e i e |   |       | <br>* | 100 | 1                          |

|----|------------------------------------------|----------------------------------------------------------------|-------------------------------|-------------------|-------------------------|------------|-----|----------|-----|---|-----|--------|-----|-----|-----|-----|-----|-------|-------|---|-------|-------|-----|----------------------------|

|    |                                          | Hardwa<br>Manual                                               |                               |                   |                         |            |     |          |     |   |     |        |     |     |     |     |     |       |       |   |       |       |     |                            |

| 2. | BOARI                                    | O OVERV                                                        | IEW                           |                   |                         |            |     |          |     |   |     |        |     |     |     |     |     |       |       |   | <br>÷ | <br>8 |     | . 3                        |

|    | 2.2.                                     | Factor<br>Addres<br>Jumper                                     | s Swi                         | tch               | se                      | tt:        | ing | s.       |     |   |     |        |     |     |     | • • | * 1 | <br>× |       |   |       | <br>× | w i | . 2                        |

|    |                                          | 2.3.1 2.3.2 2.3.3                                              | J1 MW                         | IRT               | gen                     | era        | ati | or       |     |   |     |        |     |     |     |     | × 1 |       |       |   |       |       |     | 4                          |

|    | 2.4.<br>2.5.<br>2.6.<br>2.7.             | Eprom<br>EEprom<br>DMA col<br>PHANTO                           | Comp                          | ata<br>bil        | bil                     | ty         |     |          |     |   |     |        |     |     |     |     |     |       |       | * |       |       |     | . 5                        |

| 3. |                                          | D INSTA                                                        |                               |                   |                         |            |     |          |     |   |     |        |     |     |     |     |     |       |       |   |       |       |     |                            |

|    | 3.1.<br>3.2.                             | Unpack<br>Seatin                                               | ing/I<br>g the                | nsp<br>bo         | ect                     | ing        | ] t | he       | . E |   | 317 | d.     |     |     |     |     |     |       |       |   | <br>  | <br>* |     |                            |

| 4. | MAIN                                     | TENANCE                                                        |                               |                   | :                       |            |     |          |     |   |     |        |     |     |     |     |     |       |       |   |       |       |     | . 8                        |

| 5. | THEO                                     | RY OF O                                                        | PERAT                         | ION               |                         |            | ••• |          | * * |   |     |        |     |     |     |     |     |       |       |   |       | <br>* |     | 10                         |

|    | 5. 2. 6<br>5. 3. 8<br>5. 4. 6<br>5. 5. 1 | Extende<br>Address<br>B/16 Da<br>Address<br>Battery<br>Battery | buff<br>ta tr<br>deco<br>back | eri<br>ans<br>din | ng<br>fer<br>g/M<br>ope | mo<br>lemo | ode | 5.<br>C  | h i | P | 1   | <br>oc | at  |     | on. | s.  |     | <br>  |       |   | <br>  |       | *   | 10<br>10<br>10<br>11<br>11 |

| 6. |                                          | VICAL S                                                        |                               |                   |                         |            |     |          |     |   |     |        |     |     |     |     |     |       |       |   |       |       |     | 12                         |

|    | 6.2 E                                    | Physica<br>Environ<br>Bus int<br>Part de                       | menta<br>erfac                | 1 C               | har                     | if:        | .er | i≘<br>ti | t i | C | 5 ( | IE     | E   | =/( | 59  | 6)  |     |       |       |   |       |       | •   | 12<br>12<br>12             |

# Appendices

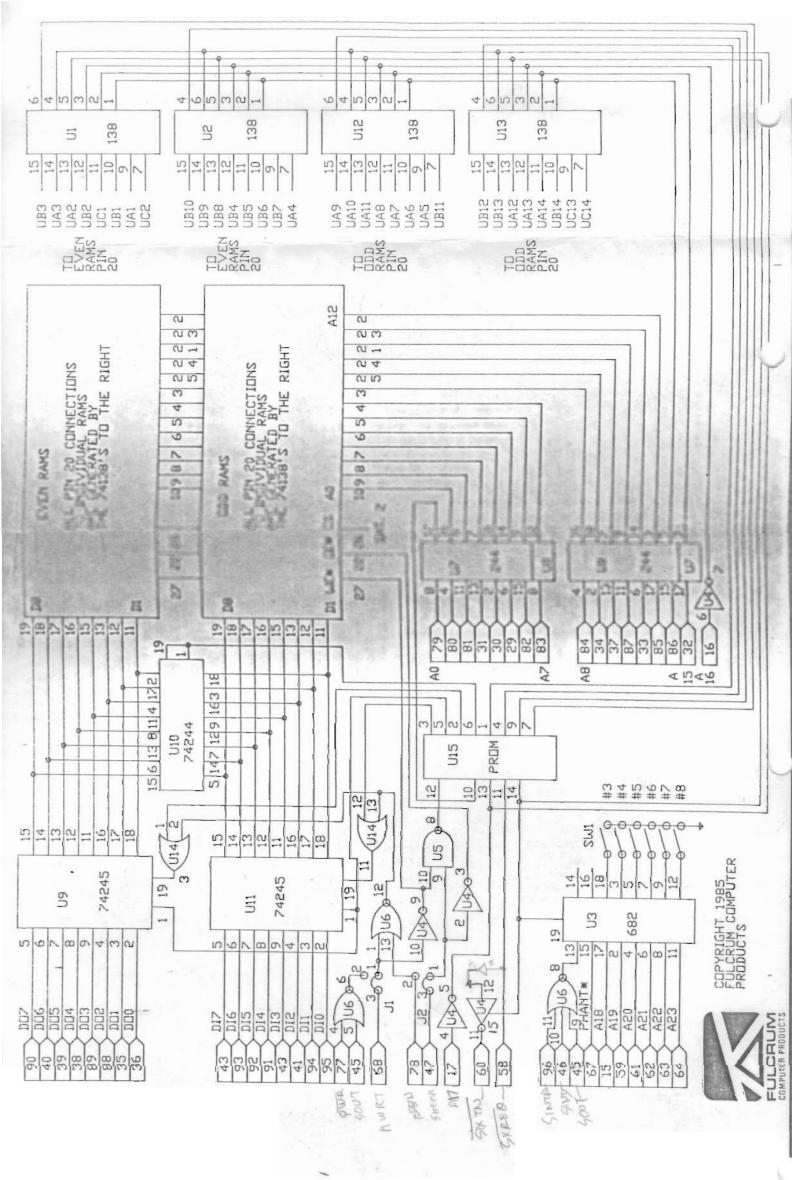

| A. | SCHEM   | ATICS |       |      |     |    |    |     |     |    |     |     |     |    |     |   |   |    |   |   |     |   |       |           | 18 |

|----|---------|-------|-------|------|-----|----|----|-----|-----|----|-----|-----|-----|----|-----|---|---|----|---|---|-----|---|-------|-----------|----|

|    |         |       |       |      |     |    | -  |     | - " |    |     |     |     |    |     | - | • |    | - | - |     | - |       |           |    |

| B. | STATE   | PROM  | LIST  | ING  |     |    |    |     |     |    |     |     |     | ٠. |     |   |   | ٠. |   | × |     |   |       |           | 20 |

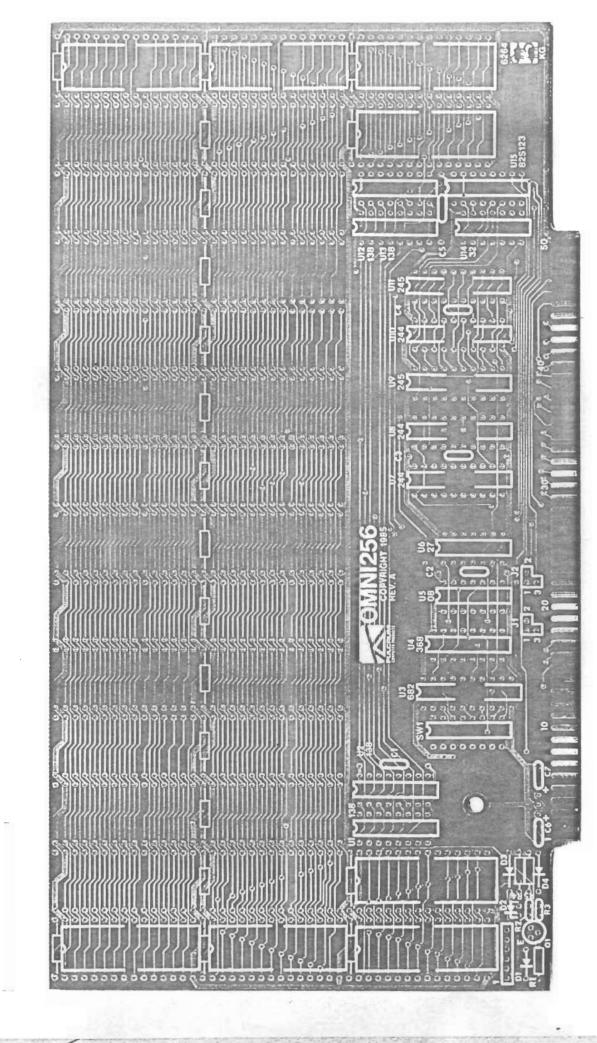

| C. | PART    | LOCAT | IONS  |      | * * |    |    |     |     |    |     |     |     |    |     |   |   |    |   |   |     |   |       |           | 21 |

|    |         |       |       |      |     |    |    |     |     |    |     |     |     |    |     |   |   |    |   |   |     |   |       |           |    |

|    |         |       |       |      |     |    |    |     |     |    |     |     |     |    |     |   |   |    |   |   |     |   |       |           |    |

|    |         |       |       |      |     |    |    | . 0 |     |    |     |     | _   |    |     |   |   |    |   |   |     |   |       |           |    |

| -  | TABLE : | 2-2 A | ddres | s de | 900 | di | ng | s   | ch  | en | nes | 5 . | o e |    | * * | * |   |    |   |   | * * | • | e; e; | <br>* . * | 2  |

|    | FODI E  | , E D | O.M   | 7 1  |     |    |    |     |     |    |     |     |     |    |     |   |   |    |   |   |     |   |       |           |    |

#### 1.0 INTRODUCTION

This manual contains the information necessary to install and operate the OMNI256 256k static ram board in an IEEE 696 environment. In addition non-standard applications and operational theory are discussed. The OMNI256 can be used under CP/M 2.2, CP/M 3.0 (CP/M+), CP/M-86, MP/M-80, MS-DOS, CCP/M (Concurrent PC-DOS), or MP/M-86.

Fulcrum Computer Products' OMNI265 board utilizes the latest in CMOS SRAM technology to provide 256 kilobytes of fast, fully static memory for IEEE-696 S-100 computer systems. This board automatically configures to 8-bit and 16-bit service requests by the host processor. Extended 24-bit addressing is supported. All assembled boards are completely factory tested.

#### 1.1. Hardware Features

The OMNI256 offers the following features:

- 1. Conforms to IEEE 696 standard. (S100 buss)

- 2. The memory can be located on any 256k boundary, and comes factory set as the first 256k in your system.

- 3. Supports 24 bit extended addressing

- The board is fully compatible with 8-bit and 16-bit data transfers, and adjusts itself dynamically.

- 5. No special considerations are required for DMA (TMA) operation due to completely static design.

- 6. Standard OMNI256 boards support 8mhz operation populated with 120ns(-12) low power(LP) parts.

- 7. Board can be phantomed with pin 67 (PHANTOM\*)

- 8. Typical Board operating power consumption of 4 watts.

- 9. Battery backup power down mode requires less than 50ua

### 2. BOARD OVERVIEW

The OMNI256 board uses a 256k linear address space starting at the base address specified by SW1. Jumpers 1 and 2 select read/write generation mode, and Jumper area B select the battery backup mode.

### 2.1 Factory Settings

Most of the jumpers present on the OMNI256 are strapped by means of traces on the P.C. board itself. Factory addressed to 00000h. It is set up to use system generated MWRT for write, sMEMR for read. This simplifies installation in a standard system. The following describes what options are available via jumpering/switch settings.

#### 2.2. Address Switch Settings

The base address switch (SW1) located on the lower left of the board, just right of the 5 volt regulator circuit. SW1.3-8 correspond to address lines A18-A23. A closed switch indicates a match on a low address line. All possible setting are listed in table 2-2, below.

Table 2-2: Switch (SW1) settings for various base addresses

| ## SW.3 SW.4 SW.5 SW.6 SW.6 SW.6 SW.6 SW.6 SW.6 SW.6 SW.6 | ! 0 | N ! ON  |

|-----------------------------------------------------------|-----|---------|

| 040000h 07ffffh My OFF! ON ! ON ! ON ! ON ! ON ! ON       | ! 0 | N ! ON  |

| 080000h 0Effffh ON ! OFF ! ON ! ON                        | ! 0 | N ! ON  |

| 080000h 0Effffh ON ! OFF ! ON ! ON                        |     |         |

|                                                           | ! 0 |         |

|                                                           |     |         |

| 100000h 13ffffh ON ! ON ! OFF ! ON                        | ! 0 | N ! ON  |

| 140000h 17ffffh OFF ! ON ! OFF ! ON                       | ! 0 | N ! ON  |

| 180000h 1Effffh ON ! OFF ! OFF ! ON                       | . 0 | NO ! ON |

| 1C0000h 1fffffh OFF! OFF! ON                              | . 0 | NO ! ON |

| 200000h 23ffffh ON ! ON ! ON ! OFF                        | ! 0 | N ! ON  |

| 240000h 27ffffh OFF ! ON ! ON ! OFF                       | ! 0 | N ! ON  |

| 280000h 28ffffh ON ! OFF ! ON ! OFF                       | : 0 | N ! ON  |

| 2C0000h 2fffffh OFF! OFF! ON! OFF                         | ! 0 | N ! ON  |

| 300000h 33ffffh ON ! ON ! OFF ! OFF                       | . 0 | N ! ON  |

| 340000h 37ffffh OFF ! ON ! OFF ! OFF                      | : 0 | N ! ON  |

| 380000h 3Bffffh ON ! OFF ! OFF                            | ! 0 | N ! ON  |

| 3C0000h 3fffffh OFF! OFF! OFF! OFF                        | ! 0 | N ! ON  |

| 400000h 43ffffh                                           | ! 0 | FF ! ON |

| 440000h 47ffffh OFF ! ON ! ON ! ON                        | . 0 | FF ! ON |

| 480000h 4Bffffh ON ! OFF ! ON ! ON                        | ! 0 | FF ! ON |

| 4C0000h 4fffffh OFF! OFF! ON! ON                          | ! 0 | FF ! ON |

| 5000000h<br>540000h<br>580000h<br>500000h    | 53ffffh<br>57ffffh<br>5Bffffh<br>5fffffh | ON !<br>OFF !<br>OFF !         | ON<br>OFF | OFF<br>OFF<br>OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ! (        | 0N<br>0N<br>0N    | !                                       | OFF<br>OFF<br>OFF |                                         | 0N<br>0N<br>0N    |

|----------------------------------------------|------------------------------------------|--------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|-----------------------------------------|-------------------|-----------------------------------------|-------------------|

| 6000000h<br>6400000h<br>6800000h<br>6000000h | 63ffffh<br>67ffffh<br>6Bffffh<br>6ffffh  | ON !<br>OFF !<br>ON !<br>OFF ! | ON<br>OFF | ON ON ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ! (        | OFF<br>OFF        | !                                       | OFF<br>OFF<br>OFF | !                                       | 0N<br>0N<br>0N    |

| 7000000h<br>740000h<br>780000h<br>7C00000h   | 73ffffh<br>77ffffh<br>7Bffffh<br>7fffffh | ON !<br>OFF !<br>OFF !         | ON<br>OFF | OFF<br>OFF<br>OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ! (<br>! ( | OFF<br>OFF<br>OFF |                                         | OFF<br>OFF<br>OFF | !                                       | 0N<br>0N<br>0N    |

| 8000000h<br>8400000h<br>8800000h<br>8C00000h | 83ffffh<br>87ffffh<br>8Bffffh<br>8fffffh | ON !<br>OFF !<br>ON !<br>OFF ! | ON        | The state of the s | ! (        | 0N<br>0N<br>0N    |                                         | ON<br>ON<br>ON    | !!!!!!!                                 | OFF<br>OFF<br>OFF |

| 900000h<br>940000h<br>980000h<br>9C00000h    | 93ffffh<br>97ffffh<br>9Bffffh<br>9fffffh | ON .<br>OFF .<br>ON .<br>OFF   | ON<br>OFF | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ! (        | ON<br>ON<br>ON    | !!!!!                                   | ON<br>ON<br>ON    | !                                       | OFF<br>OFF<br>OFF |

| A00000h<br>A40000h<br>A80000h<br>AC0000h     | A3ffffh<br>A7ffffh<br>ABffffh<br>Afffffh | ON !<br>OFF !<br>ON !          | ON<br>OFF | ON<br>ON<br>ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ! (        | OFF<br>OFF<br>OFF | !!!!!                                   | ON<br>ON<br>ON    | !!!!!!                                  | OFF<br>OFF<br>OFF |

| B00000h<br>B40000h<br>B80000h<br>BC0000h     | B3ffffh<br>B7ffffh<br>BBffffh<br>Bfffffh | ON !<br>OFF !<br>OFF !         | ON<br>OFF | OFF<br>OFF<br>OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ! (<br>! ( | OFF<br>OFF<br>OFF | !                                       | ON<br>ON<br>ON    | !!!!!                                   | OFF<br>OFF<br>OFF |

| C000000h<br>C40000h<br>C80000h<br>CC00000h   | C3ffffh<br>C7ffffh<br>CBffffh<br>Cfffffh | ON !<br>OFF !<br>ON !<br>OFF ! | ON<br>OFF | ON<br>ON<br>ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ! (        | ON<br>ON<br>ON    | !                                       | OFF<br>OFF<br>OFF | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | OFF<br>OFF<br>OFF |

| D000000h<br>D40000h<br>D80000h<br>DC00000h   | D3ffffh<br>D7ffffh<br>DBffffh<br>Dfffffh | ON !<br>OFF !<br>ON !          | ON<br>OFF | OFF<br>OFF<br>OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ! (        | 0N<br>0N<br>0N    | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | OFF<br>OFF<br>OFF | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | OFF<br>OFF<br>OFF |

| E00000h<br>E40000h<br>E80000h<br>EC0000h     | E3ffffh<br>E7ffffh<br>EBffffh<br>Efffffh | ON !<br>OFF !<br>ON !          | ON        | ON<br>ON<br>ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ! (<br>! ( | OFF               | !!!!                                    | OFF<br>OFF<br>OFF | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | OFF<br>OFF<br>OFF |

| F00000h<br>F40000h<br>F80000h<br>FC0000h     | F3ffffh<br>F7ffffh<br>FBffffh<br>FFFFFFh | ON !<br>OFF !<br>OFF !         | ON<br>OFF | OFF<br>OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ! (<br>! ( | OFF               | 1.                                      | OFF<br>OFF        | !!!!!!                                  | OFF<br>OFF<br>OFF |

### 2.3. Jumper Settings

There are 3 jumper areas on the OMNI256. Description/usage of each follows. Refer to APPENDIX C for help in locating, if needed.

#### 2.3.1. Battery Backup Options

This section refers to jumper area 'B', located on the left lower corner of the OMNI256. It has six pins, numbered from left to right as 1-6. Shunt pins 1-2 if not using battery backup, otherwise leave open and jumper the other pins as follows:

Jumper 5-6 is for trickle charging your battery. Shunt if using a chargeable battery. Warning: Do not shunt this if the battery type you are using is non chargeable, i.e lithium or alkaline.

Pins 3-4 connect to the battery. Pin 3 connects to the (-) negative end of battery. Pin 4 is the positive connection.

Refer to the theory of operation for consideration of various battery types.

#### 2.3.2. J1 - MWRT generation

This jumper is located near the edge connector just left of the silk screened marking for S100 buss pin 20. It is used to configure the board to use either system generated MWRT or to generate MWRT from sOUT and pWR for local use. To use system MWRT shunt pins 1-3 on J1. For board generated MWRT shunt pins 1-2. Board generation of MWRT does not affect system MWRT signal. This jumper is factory configured for system MWRT use. If a change is necessary then a trace may need to be cut on the solder side of the board. This is primarily intended for systems that do not generate MWRT.

## 2.3.3. J2 - sMEMR or pDBIN data reads

This jumper is located near the edge connector just right of the silk screened marking for S100 buss pin 20. It is used to configure determine what signal the OMNI256 is to use for write generation.

#### 2.4. EPROM COMPATIBILITY

The pinout of the HM 6264 LP -12 is pin-for-pin compatible for use with industry standard 2764 type EPROM devices. Due to the OMNI256 compatibility with 16-bit wide data transfers, odd and even memory locations are stored in to physically different devices. Due to this pairing requirement, the minimum ROM area is 16k bytes. i.e. two 2764's occupying two socket positions. For placement/ address decoding considerations, check section 5.4. Power and speed considerations may apply depending on device type utilized.

### 2.5. EEPROM Compatibility

There are several EEPROM devices available that latch addresses and data for writing (i.e X2864A by Xicor), and therefore could potentially be utilized. Power and speed considerations apply.

#### 2.6. DMA (TMA) Considerations

This card does not have restrictions as to the length of a DMA operation, since it is static by design.

#### 2.7. PHANTOM\* usage

This card is not selectable on assertion of PHANTOM\*. This is used primarily for booting purposes. For example, a disk controller may need to have a boot prom resident in the memory image that is also occupied by the OMNI256. The conflict is resolved by the disk controllers' assertion of PHANTOM\*, and forcing the OMNI256 to deselect.

#### 3.0 BOARD INSTALLATION

This portion of the manual provides instructions for preparing and installing your OMNI256. Unpacking and inspection instructions are included, as are instructions for setting up the jumper and switch options.

#### 3.1 Unpacking and Inspection

All computer cards must be handled with care, since the components on them may be damaged by bending or bumping. Also the chips may come loose if the board is mishandled.

You should be especially careful of static electricity when you handle the OMNI256 board, since the memory chips are of CMOS technology and susceptible to damage from static. Discharge any static that has built up on your body by touching an electrically grounded piece of metal (such as other grounded equipment, or a metal desk) before handling the board. For added safety keep the board in its' conductive envelope during transportation or handling.

Upon receipt of your OMNI256, immediately inspect the shipping carton and the board itself for evidence of mishandling or damage during transit. If the shipping container is severly damaged or waterstained, contact the carrier and request that his agent be present when any additional cartons are opened. If the carton is opened and the carrier's agent is not present, save the carton and all shipping materials for the agent's inspection.

The shipping carton and packing material have been carefully designed to protect the OMNI256 during shipment. If it becomes necessary to return a board, it should be repacked in its original shipping carton with its original packing material.

Check that all chips are seated in their sockets. If a chip is not fully seated in its socket, be sure that all of the pins of the chip are above the holes in its socket. Push gently on the end that is sticking up from the board until the chip is evenly flat against the socket.

Also, be sure that the black rectangular jumpers connectors that stand above the board are pushed all the way down on their jumper pins. If any of the jumpers have fallen off the board, read the next section and replace them on the correct pins.

#### 3.2. Seating the Board

Once you are certain that the jumpers are set correctly, install the board in your system. Make sure that the computer is not plugged on. Do not install or handle this board with the system on, as this may cause damage to the board components, traces, and other boards in your system.

Slide the board in any free slot on the motherboard, making sure the component side is oriented correctly. Gently push the top of the board until the board is seated in the motherboard.

If you need to remove the board, pull gently on the top of board and rock it to loosen it from the edge connector, then simply pull up.

## 4. MAINTENANCE

Once past burn-in it is unlikely that this card will require any maintenance. If your computer system reports that there is a bad byte of RAM on the board, use the table 4-5 to determine which chip may be the culprit.

| cccc                           | BBBBBB                         | AAAAAA                               |

|--------------------------------|--------------------------------|--------------------------------------|

| Even UC01<br>  +20000 to 23FFF | Even UB01<br>  +24000 to 27FFF | Even UA01  <br>  +28000 to 2BFFF   : |

|                                |                                | Even                                 |

|                                |                                | Even UA03  <br>  +34000 to 37FFF   3 |

|                                | +10000 to 1FFFF                | Even                                 |

|                                |                                | Odd                                  |

|                                |                                | Odd                                  |

|                                | +08000 to 0BFFF                | Odd                                  |

| map                            | +18000 to 1BFFF                | Odd                                  |

|                                | I Even UB09                    | Odd                                  |

| •                              |                                | Odd                                  |

|                                |                                | Odd                                  |

| . 3                            |                                | Odd                                  |

|                                |                                | Odd                                  |

|                                |                                | Odd                                  |

### 5. THEORY OF OPERATION

The OMNI256 memory board conforms to the IEEE-696/ S-100 standards for memory devices. This section assumes that the reader has some experience in logic circuitry.

Because the OMNI256 is a static memory which does not require refresh cycles to preserve the contents of memory, its operation is somewhat simple and straightforward.

#### 5.1 Board select generation

U3, an 8-bit comparator is used to generate BDSEL\* an active low signal indicating that the address on the host buss is within the memory reserved for this board, and that we are not doing an IO cycle. PHANT\*, SINTA\* also prevent BDSEL\* activation from U3. If the board is selected (BDSEL\*) then SIXTN is forced high, indicating that we are capable of 16-bit transfer, the state rom (U15) is activated, along with U1-2, U12-13, the ram select drivers. If PHANTOM\* is low (active) then BDSEL\* will not occur.

## 5.2 Address buffering

The address lines AO-A15 (16 lines) are buffered through schmitt trigger type buffers (U7, U8) to drive the ram array. A16 is buffered through U4, this selects which pair of 138's will be active.

### 5.3. 8-bit/16-bit bus operation

The OMNI256 has two internal data paths or busses. All of the memory chips which are addressed when AØ is true are connected to one bus (ODD bus), while those chips which are addressed when AØ is false are connected to another bus (EVEN bus).

A bipolar PROM, U15, generates from A0, sXTRG (16-bit data transfer request from host), and sMEMR the proper logical arrangement of the ODD/EVEN data paths.

U10 acts as a multiplexor for the odd/even busses converging their output to D00-7. For even 8-bit reads, the data flows through from the even ram array do cross-link buffer U9 (74LS245) and out to the host. Odd 8-bit read is similar; The data flows from the odd data path through buffer U10 (74LS244) and then out to the system buss.

For an 8-bit write operation U11 (74LS245) buffers the data incoming from the system buss, and this is channeled to either the even bank, if U10 (74LS244) is enabled, or the odd bank if U10 is not enabled.

For 16-bit bus operation the cross-link buffer U10 is remains disabled for both reads and writes. The Odd data is buffered by U11 (74LS245) to/from the ODD data buss. The even data is buffered by U9 (74LS245) to/from the EVEN data buss. This occurs simultaneously for 16-bit operation.

The proper select/direction signals are generated by U15 (TBP18SØ3Ø) depending on the current state of the host buss. Bus contention glitches are avoided by enabling the S-10Ø bus buffers U9 and U11 only after the internal bus connections have been established. This is possible because sMEMR which determines whether or not the cycle is to a read or a write is established before pDBIN/MWRT is asserted.

#### 5.4. RAM select routing

The address lines A17\*, A16\*, A14, A15, along with the four select lines (SELØ-3) generated by U15, and BDSEL\* are routed to the RAM select decoders U1, U2, U12, and U13. This maps the memory devices as per table 4-5.

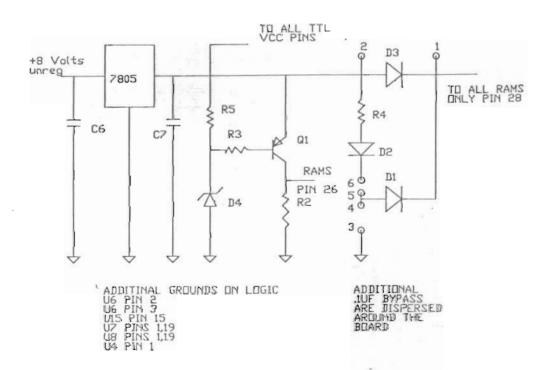

#### 5.5. Battery backup operation

Battery backup operation is convened through the use of low power CMOS static ram, and some simple circuitry. During normal power operation the R5-D4 junction is at 4.3v which biases Q1 into a conducting region, and thereby the collector is at a logic high equivalent. This drives pin 26, common to all rams, high.

When a power drop (power failure or normal shutdown) occurs Q1 no longer conducts, and pin 26 is pulled low by R2. This signals the rams to go into power-down mode.

Further, diode D3 prevents the backup battery from powering anything but the ram chips on power down. Diode D1 is used to prevent the battery from charging from the logic supply. If pins 5-6 are shunted then the battery is charged through R4 and D2 from the logic supply. Diode D3 is a hot carrier type to reduce forward voltage drop to a few millivolts.

#### 5.6 Backup Battery Selection

There are quite a few choices for the type of backup battery. We suggest the use of lithium. It requires no charging, and is low maintenance. NiCd may be used, but the time between power ons is seriously compromised. This is due to a loss of 1%/day of NiCd charge. A minimum of three NiCd cells are required to meet the minimum backup voltage requirement of 3 volts (3 \* 1.2 = 3.6). Other candidates include Gel Cell and Alkaline. Alkaline batteries are not as long lasting as Lithium-Manganese Oxide systems, but they are much cheaper. Use of higher voltages increases power requirements and may shorten battery life.

## 6.0 ENGINEERING SPECIFICATIONS

#### 6.1 PHYSICAL CHARACTERISTICS

The OMNI256 is a single height card that occupies one card position in an S100 motherboard.

#### 6.2 ENVIRONMENTAL CHARACTERISTICS

Temperature:

Operating

0 C to +50 C

Non-operating

-50 C to +85 C

Humidity:

Operating: up to 90% relative humidity without

condensation.

Non-operating: all conditions without condensation or

frost.

6.3 DC Power Requirements

operating characteristics

+8 volts

500ma maximum

battery backup mode characteristics

+3.0 volts

50ua maximum

10ua typical

## 6.4 - IEEE 696/ S100 specifications

All signals are TTL level except where noted and follow the usual convention of a low voltage being 0 or FALSE and a high voltage being a 1 or TRUE. Signals that are active low follow the opposite convention and are denoted by the \* suffix. Inputs For complete timing specifications refer to the IEEE-696 standard document: Standard specifications for S100 bus interface devices IEEE task 696.1/ D2.

## Pin NO. Signal Mnemonic Description

| 1  | +8 Volts | Instantaneous minimum greater than 7 volts<br>Instantaneous maximum less than 25 volts<br>Average maximum less than 11 volts |

|----|----------|------------------------------------------------------------------------------------------------------------------------------|

| 4  | VIO*     | Vectored interrupt line 0.                                                                                                   |

| 5  | VI1*     | Vectored interrupt line 1.                                                                                                   |

| 6~ | VI2*     | Vectored interrupt line 2.                                                                                                   |

| 7  | VI3*     | Vectored interrupt line 3.                                                                                                   |

| 8  | VI4*     | Vectored interrupt line 4.                                                                                                   |

| 9  | VI5*     | Vectored interrupt line 5.                                                                                                   |

| 10 | VI6*     | Vectored interrupt line 6.                                                                                                   |

| 11 | VI7*     | Vectored interrupt line 7.                                                                                                   |

| 12 | NMI*     | Non-maskable interrupt.                                                                                                      |

| 15 | A18      | Extended address bit 18                                                                                                      |

| 16 | A16      | Extended address bit 16                                                                                                      |

| 17 | A17      | Extended address bit 17                                                                                                      |

| 24 | Φ.       | The master timing signal for the bus.                                                                                        |

| 29 | A5       | Address bit 5                                                                                                                |

| 30 | A4       | Address bit 4                                                                                                                |

| 31 | A3       | Address bit 3                                                                                                                |

| Address bit 15  Address bit 12  Address bit 9  D01/DATA1 Data out bit 1, bidirectional data  D00/DATA0 Data out bit 0, bidirectional data  A10 Address bit 10  BD04/DATA4 Data out bit 4, bidirectional data  D05/DATA5 Data out bit 5, bidirectional data  D05/DATA6 Data out bit 6, bidirectional data  D12/DATA10 Data in bit 2, bidirectional data  D13/DATA11 Data in bit 3, bidirectional data  D17/DATA15 Data in bit 7, bidirectional data  A3 D17/DATA15 Data in bit 7, bidirectional data  A4 SM1 The status signal which indicates the current cycle is an op-code of transfer bus cycle to an output of transfer bus cycle to an output of transfer bus cycle from an input of transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal which acknowledge instruction fetch cycle(s)  A8 SHLDA The status signal which acknowledge instruction has been executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | a bit 0 a bit 4 a bit 5 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| A9 Address bit 9  35 D01/DATA1 Data out bit 1, bidirectional data 36 D00/DATA0 Data out bit 0, bidirectional data 37 A10 Address bit 10  38 D04/DATA4 Data out bit 4, bidirectional data 39 D05/DATA5 Data out bit 5, bidirectional data 40 D06/DATA6 Data out bit 6, bidirectional data 41 D12/DATA10 Data in bit 2, bidirectional data 42 D13/DATA11 Data in bit 3, bidirectional data 43 D17/DATA15 Data in bit 7, bidirectional data 44 SM1 The status signal which indicates the current cycle is an op-code for south of transfer bus cycle to an output described by the status signal identifying the data signal identifying bus considered by the status signal which acknowledge by | a bit 0 a bit 4 a bit 5 |

| Data out bit 1, bidirectional data  Data out bit 0, bidirectional data  Al0 Address bit 10  Data out bit 4, bidirectional data  Data out bit 4, bidirectional data  Dos/DATA5 Data out bit 5, bidirectional data  Dos/DATA6 Data out bit 6, bidirectional data  Dos/DATA6 Data out bit 6, bidirectional data  Dis/DATA10 Data in bit 2, bidirectional data  Dis/DATA11 Data in bit 3, bidirectional data  Dis/DATA15 Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code of transfer bus cycle to an output described by transfer bus cycle from an input described by the status signal identifying the described by the status signal identifying the described by the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which transfer data from memory the status signal identifying bus of which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a bit 0 a bit 4 a bit 5 |

| Data out bit 0, bidirectional data Address bit 10  Bata out bit 4, bidirectional data Dos/DATA4  Data out bit 5, bidirectional data Dos/DATA5  Data out bit 6, bidirectional data Dos/DATA6  Data out bit 6, bidirectional data Dis/DATA10  Data in bit 2, bidirectional data Dis/DATA11  Data in bit 3, bidirectional data Dis/DATA15  Data in bit 7, bidirectional data Dis/DATA15  Data in bit 7, bidirectional data  Mata Dis/DATA15  Data in bit 7, bidirectional data Disymptotic bid in dicates the current cycle is an op-code of the current cycle is an op-code of the current bid bid indicates the current cycle is an op-code of the current bid bid indicates the current cycle is an op-code of the current bid bid indicates the current cycle is an op-code of the current bid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | a bit 0 a bit 4 a bit 5 |

| Address bit 10  38 D04/DATA4 Data out bit 4, bidirectional data 39 D05/DATA5 Data out bit 5, bidirectional data 40 D06/DATA6 Data out bit 6, bidirectional data 41 DI2/DATA10 Data in bit 2, bidirectional data 42 DI3/DATA11 Data in bit 3, bidirectional data 43 DI7/DATA15 Data in bit 7, bidirectional data 44 SM1 The status signal which indicates the current cycle is an op-code for south of transfer bus cycle to an output described by the status signal identifying the described by the status signal identifying the described by the status signal identifying the described by the status signal identifying bus described by the status signal which acknowledge status status signal which acknowledge s | a bit 4<br>a bit 5      |

| Data out bit 4, bidirectional data  Data out bit 5, bidirectional data  Dos/DATA5  Data out bit 5, bidirectional data  Dos/DATA6  Data out bit 6, bidirectional data  Dis/DATA10  Data in bit 2, bidirectional data  Dis/DATA11  Data in bit 3, bidirectional data  Dis/DATA11  Data in bit 7, bidirectional data  Dis/DATA15  Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code of  Dos Dut  The status signal identifying the data transfer bus cycle to an output data  The status signal identifying the data stansfer bus cycle from an input data  The status signal identifying bus of which transfer data from memory the master, which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | a bit 5                 |

| Data out bit 5, bidirectional data  Docompared Data out bit 6, bidirectional data  Docompared Data out bit 6, bidirectional data  Docompared Data in bit 2, bidirectional data  Docompared Data in bit 3, bidirectional data  Docompared Data in bit 3, bidirectional data  Docompared Data in bit 7, bidirectional data  Docompared Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code of the current cycle is an op-code of the current bus cycle to an output of the status signal identifying the data from memory the status signal identifying bus of the cycle of the cycle of the status signal identifying bus of the cycle of the cycle of the status signal identifying bus of the cycle of the cycle of the status signal which are not interrupt a instruction fetch cycle of the status signal which acknowledge of the cycle of the status signal which acknowledge of the cycle of the cycle of the status signal which acknowledge of the cycle o | a bit 5                 |

| Data out bit 6, bidirectional data DI2/DATA10 Data in bit 2, bidirectional data DI3/DATA11 Data in bit 3, bidirectional data DI7/DATA15 Data in bit 7, bidirectional data  M1 The status signal which indicates the current cycle is an opecode of the current cycle is an opecode of the status signal identifying the data signal identifying bus cycle from an input data signal signal identifying bus cycle from an input data signal signal identifying bus cycle from an input data signal s |                         |

| Data in bit 2, bidirectional data  DI3/DATA11  Data in bit 3, bidirectional data  DI7/DATA15  Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code for transfer bus cycle to an output described transfer bus cycle from an input described transfer data from memory the master, which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge  Bata in bit 2, bidirectional data  Di3/DATA11  Data in bit 2, bidirectional data  The status signal which indicates the cycle of the cycle o | bit 6                   |

| DI3/DATA11 Data in bit 3, bidirectional data  DI7/DATA15 Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code for the current cycle is an op-code for the status signal identifying the data transfer bus cycle to an output described for the status signal identifying the data from an input described for the status signal identifying bus cycle from an input described for the status signal identifying bus cycle from an input described for the status signal identifying bus cycle from memory the status for the status for memory the status for memo |                         |

| Data in bit 7, bidirectional data  The status signal which indicates the current cycle is an op-code for the current cycle is an op-code for transfer bus cycle to an output described for transfer bus cycle to an output described for transfer bus cycle from an input described for transfer data from memory the described formula for transfer data from memory the described formula for transfer data from memory the described formula for the status signal which are not interrupt a described formula for the status signal which acknowledged for the | a bit 10                |

| The status signal which indicates to the current cycle is an op-code of the cycle to an output of the status signal identifying the distribution to the cycle from an input of the cycle from an input of the cycle from | a bit 11                |

| the current cycle is an op-code f  The status signal identifying the d transfer bus cycle to an output d  The status signal identifying the d transfer bus cycle from an input d  The status signal identifying bus c which transfer data from memory t master, which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | a bit 15                |

| The status signal identifying the d transfer bus cycle to an output d  The status signal identifying the d transfer bus cycle from an input d  The status signal identifying bus c which transfer data from memory t master, which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |

| transfer bus cycle from an input d  47 SMEMR The status signal identifying bus of which transfer data from memory to master, which are not interrupt a instruction fetch cycle(s)  48 SHLDA The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| which transfer data from memory to master, which are not interrupt a instruction fetch cycle(s)  The status signal which acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |