Viasyn Corporation 26538 Danti Court, Hayward, CA 94545-3999 (415) 786-0909

\$20.00 8261-0031B

196125A/1

# SP186 TECHNICAL MANUAL

HIGH PERFORMANCE 80186

512-KBYTE RAM

DUAL ASYNCHRONOUS COMMUNICATION CHANNELS

SP186 TECHNICAL MANUAL Copyright 1986 Viasyn Hayward, CA 94545

Document No. 8261-0031B Filename: SP186.MAN Board No: 366A

DISCLAIMER - Viasyn Corporation makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, VIAYSN reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of VIASYN to notify any person of such revision or changes.

Trademarks: SP186, SPUZ; Viasyn Corporation. CP/M-68K, CP/M-80; Digital Research.

Registered Trademarks: CompuPro; Viasyn Corporation. CP/M, CP/M-86, Concurrent CP/M; Digital Research.

Compound Trademarks: CP/M 8-16, Concurrent DOS 8-16; Viasyn Corporation and Digital Research.

All rights reserved. No part of this publication may be reproduced or transmitted in any form, or by any means, without the written permission of VIASYN. Printed and assembled in the United States of America.

### Contents

| Specii    | ications                                                                | 1                     |

|-----------|-------------------------------------------------------------------------|-----------------------|

| About     | the SP186                                                               | 1                     |

| Introd    | uction to Slave Processing                                              |                       |

|           | The SP186 as an I/O Processor                                           | 3                     |

|           | The SP186 an an Execution Unit                                          | 3 3                   |

| You and I | Handle CD104 David                                                      |                       |

| Instai    | ling the SP186 Board                                                    |                       |

|           | Step 1. Unpack the SP186 Board.<br>Step 2. Install the Card Extractors. | 6                     |

|           | Step 3. Check Switch and Jumper Settings                                |                       |

|           | Step 4. How to Install Jumper Shunt Connectors                          | 7                     |

|           | Step 5. Insert the SP186 into the S-100 Bus.                            | 7<br>7<br>7<br>8<br>9 |

|           | Switch and Jumper Summary                                               | - 0                   |

|           | Switch Settings                                                         | 0                     |

|           | Jumper Settings                                                         |                       |

|           | Jumper Settings                                                         | 11                    |

| Theor     | y of Operation                                                          |                       |

|           | References                                                              | 14                    |

|           | Overview                                                                | 14                    |

|           | Clock Generation                                                        | 15                    |

|           | DRAM Refresh                                                            | 15                    |

|           | The DUART Ports                                                         | 16                    |

|           | S-100 Access to SP186 Memory                                            | 16                    |

|           | SP186 Control Ports                                                     | 16                    |

|           | SP186 Initialization                                                    | 19                    |

|           | 80186 Reset                                                             | 19                    |

|           | Interrupts                                                              | 19                    |

|           | Memory Addressing on a 32 Kbyte Boundary by                             |                       |

|           | Host Processor                                                          | 20                    |

|           | The DUART Input and Output Bits                                         | 21                    |

|           | DRAM Parity Checking                                                    | 23                    |

|           | Multi-tasking                                                           | 24                    |

|           | Dual Ported Memory Arbitration                                          | 25                    |

|           | SP186 Internal Timing                                                   | 26                    |

| Progra    | amming for the SP186                                                    |                       |

|           | Introduction                                                            | 27                    |

|           | SP186 Hardware Initialization                                           | 27                    |

|           | Refresh                                                                 | 28                    |

|           | 80186 Sample Listing                                                    | 28                    |

| Schem     | atic Diagrams                                                           | 30                    |

| Parts     | List                                                                    | 37                    |

| C         |                                                                         |                       |

| Compo     | onent Layout                                                            | 39                    |

| Appendix A                  |    |

|-----------------------------|----|

| The DUART                   | 40 |

| Appendix B                  |    |

| SP186 Sample Code           | 54 |

| Warranty Information        | 7  |

|                             |    |

| List of Tables              |    |

| Table 1: Jumper Functions   | 8  |

| Table 2: Switch Functions   | 9  |

| Table 3: I/O Port Selection | 13 |

| Table 4: SP186 Port Map     | 17 |

| Table 5: PORTL* Bit Map     | 18 |

| Table 6: DRAM Addressing    | 21 |

Table 9: 80186 Memory Map with BANK\* Negated

Table 10: 80186 Memory Map with BANK\* Asserted 25

23

Table 7: Output Bits of the 2681

Table 8: Input Bits of the 2681

# Specifications

Timing . . . . . . Meets all IEEE 696/S-100 specifications

Processor . . . . . 80186

Clock Rate . . . . 10 MHz

Memory . . . . . 512 Kbytes of RAM

S-100 Address Space . Occupies 64-Kbyte memory space and 2 I/O ports

S-100 Memory Address . Switch selectable to any 64-Kbyte page

Data Bus Width . . 16 bits internal, and fully conforms to IEEE 696/S100 16-bit protocol

Power Consumption . . 2000 mA typical, 2500 mA maximum

### About the SP186

The CompuPro SP186 Slave Processing Unit (80186) represents a significant advancement in multi-processing within the IEEE 696/S-100 environment. The SP186 combines a 10 MHz 80186, 512 Kbytes of memory, and two fully bi-directional RS-232C serial I/O channels to perform a number of "slave processing" tasks.

The SP186 supplies a high performance 16-bit node for a multi-user, multi-processing environment. Users can have their own 80186 processor, 512 Kbytes of memory, and their own serial ports. When used as an execution unit, the SP186 runs 16-bit user programs, dramatically reducing the requirements on the host. When used as a front-end 1/O processor, the SP186 acts as an autonomous computer with serial ports, with access to all the resources of the host through operating system calls. Up to sixteen SP186s can reside within the same mainframe.

The SP186 is ideal for adding additional 16-bit processing power to 16-bit processor based systems. It is also ideal for adding 16-bit capability to 32-bit processor based systems. Where high throughput is necessary, this multiprocessing configuration, in which host and slaves run simultaneously, is clearly superior to earlier dual processing systems where one of the processors is stopped while the other is running.

The SP186 meets all IEEE 696/S-100 bus specifications and is designed to run in S-100 based systems running at 10 MHz and up.

### Features include:

- 10-MHz, 16-bit 80186 for high throughput

- 512 Kbytes of on-board RAM: sixteen SP186 boards occupy only 64 Kbytes of system memory

- · Parity generation and detection for high reliability

- Dual bi-directional, asynchronous RS-232C serial ports for operation up to 38.4 Kbaud

- Fully software-selectable serial port parameters

- Supported by CompuPro's Concurrent DOS 8-16<sup>tm</sup> multi-user, multi-tasking operating system and by CP/M-68K<sup>tm</sup>

- · True multi-processing instead of dual-processing

- 16-bit node in a "processor-per-user" system

- 16-bit capability in 16-bit and 32-bit systems

# Introduction to Slave Processing

Tasks on a computer can be divided into two categories:

- · I/O, including character and disk

- · Execution of user programs

The SP186 is designed to process either character I/O or user programs effectively by dynamically changing roles under software control. When handling character I/O through its dual UART (DUART), the SP186 (80186, memory, and DUART) is in front-end I/O processor mode. When executing programs for the user, the SP186 is in execution unit mode. Due to the ability to change roles, the SP186's internal processor can timeshare between these two operations.

The major physical difference between these two modes is whether or not the task uses the on-board DUART.

### The SP186 as an I/O Processor

When the SP186 is used as a front-end I/O processor, the task running on the SP186 uses the DUART for character I/O. It may also use the host for disk and character I/O through operating system calls.

Applications that use the SP186 as a front-end I/O processor require custom software that makes direct use of the DUART. Software development for custom applications can be done in a standard CP/M-86 format using the standard CP/M<sup>®</sup> tools (assemblers and debuggers) running on the SP186.

## The SP186 as an Execution Unit

When the SP186 is used as an execution unit, any process running on the SP186 uses only system I/O; that is, it performs all of its character and disk I/O through the host CPU using operating system calls.

For example, the SP186 runs CP/M-86® programs as an execution unit. The 16-bit program is loaded into the SP186 and run by invoking SW86.CMD or SW86.68K under CompuPro's Concurrent DOS 8-16 or CP/M-68K, respectively. When the program requests disk or character I/O through CP/M-86 calls, the host provides it by using its I/O channels (terminals or disks).

One application of the SP186 in the front-end processor mode would be to monitor a stream of serial communication. Data would be brought in through a UART, processed by the 80186, and then retransmitted by the UART. It could change data under certain conditions, or collate statistics about the data stream and transfer these statistics to the host. Multiple SP186s can be used under one host, in one computer, to monitor many links.

Another way to think of the SP186 in the front-end processor mode is simply as an 80186 with a DUART and RAM, with two important additions:

- It can access the full resources of the host computer (e.g., disk) through operating system calls.

- The host computer can load the SP186 with programs. Any application in this category will use the Dual UART on the SP186 for communication.

In the execution unit mode, programs invoked by a user from the command line are loaded into the SP186 and executed. Input to the program can be from the system disk or system I/O ports through operating system (OS) calls. The input is acted upon by the program within the SP186, and the output is channeled back to the system disk or system I/O ports. For example, the SP186 is able to run 16-bit code that was written to operate under CP/M-86, on a host computer that may not support CP/M calls or doesn't run 16-bit 8086-type code (68000 or 32016 based systems). Another use is to add 16-bit multi-processing power to a 16-bit system that is heavily loaded.

An ideal application for the SP186 as an execution unit is as an upgrade to an existing multi-user CompuPro system running Concurrent DOS 8-16. In a system where the central CPU is bogging down under heavy loads, the SP186 can be added to enhance 16-bit performance. In addition, the SP186 relieves the host CPU of user programs, allowing it to execute the operating system functions more quickly and efficiently.

Another key application for the SP186 is found in systems where multiple tasks require large blocks of memory. Because the I Mbyte maximum addressable memory space of 8086 based uni-processor systems limits the number of programs that can be run, the SP186 provides an avenue for continued expansion of the memory space. Since each SP186 has 512 Kbytes of RAM, and sixteen SP186s can be in a system, far more memory is available to execute 16-bit programs.

A final application for the SP186 as an execution unit is to run 16-bit 8086-type code in a system that has a non-8086-type processor as a host. The SP186 can be installed in CompuPro 68K based systems running CP/M-68K to give the system the ability to run CP/M-86 programs. Thus, in a development environment, editing can be done on the SP186 using a CP/M-86 word processor such as 16-bit NewWord<sup>tm</sup>, and compilation and debugging can be done by the host 68K processor. Finally, a CompuPro 68K system with a CompuPro Z80H based SPUZ<sup>tm</sup> and CompuPro SP186 can run CP/M-68K (68000), CP/M-86 (80186), and CP/M-80<sup>tm</sup> (Z80) programs.

# Installing the SP186 Board

### Step 1. Unpack the SP186 Board.

Along with the board, you will find extra jumper shunts and two card extractors in the plastic bag.

CARD EXTRACTOR

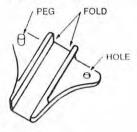

### Step 2. Install the Card Extractors.

- 1. Hold the board so the component side is toward you. (See diagram below.)

- 2. Insert the peg on the card extractor into the hole in the <u>right</u> corner of the board. Fold the extractor over the board's edge until the extractor's hole snaps over the peg.

- 3. NOTE: Make sure the long edge of the extractor is along the top edge of the board.

Repeat for left extractor.

# Step 3. Check Switch and Jumper Settings

For standard switch and jumper settings for use with Concurrent DOS 8-16, refer to the Concurrent DOS 8-16 Installation and Customization Guide. For standard switch and jumper settings for use with CP/M-68K, refer to the CP/M-68K Installation and Customization Guide.

See Step 4 if you need to change jumper settings. Otherwise proceed to Step 5.

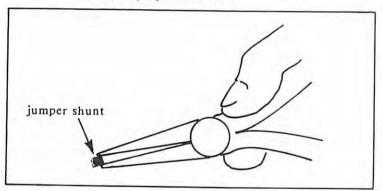

# Step 4. How to Install Jumper Shunt Connectors

A jumper shunt is a small plastic part used to connect two pins on the jumper connector. Jumper shunts should be installed notch side up.

IF: The board is not correctly jumpered.

THEN: Use a pair of needle nose pliers to gently remove, and carefully replace the jumper shunt in its proper location.

Step 5. Insert the SP186 into the S-100 Bus.

The power to the system must be off. Place the board into a slot towards the middle of the enclosure. The edge connector is offset, so the SP186 fits only one way. Push down GENTLY until the board is firmly installed.

### Switch and Jumper Summary

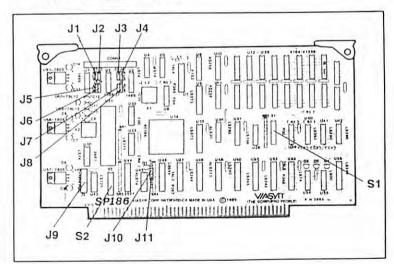

The following summary of switches and jumpers explains the function and logic of each option. For help in locating a switch or jumper, refer to the component layout diagram at the end of this manual.

The abbreviations under "RS-232 pin" are from the EIA (Electronic Industries Association) RS-232C standard, and are listed with their pin numbers. The abbreviations under "UART pin" are from the 2681 UART data sheet.

- TxD stands for transmitted data from the UART

- · RxD stands for received data into the UART

- the OPx bits are output bits from the UART

- the IPx are input bits to the UART

- · DCE stands for data communication equipment

- DTE stands for data terminal equipment

Table 1: Jumper Functions

| J<br>_ | Position | RS pir |   | 32   | UAR' |   | SP186<br>function |         |

|--------|----------|--------|---|------|------|---|-------------------|---------|

| 1      | A-C      | ВВ     | A | (3)  | TxD  | Α | DCE               | )       |

|        | B - C    | BB     | A | (3)  | RxD  | A | DTE               | Channel |

| 2      | A-C      | BA     | A | (2)  | TxD  | Α | DTE               | A       |

|        | B - C    | BA     | Α | (2)  | RxD  | Α | DCE               | ).      |

| 3      | A-C      | ВВ     | В | (3)  | TxD  | В | DCE               | 1       |

|        | B - C    | BB     | В | (3)  | RxD  | В | DTE               | Channel |

| 4      | A-C      | BA     | В | (2)  | TxD  | В | DTE               | В       |

|        | B - C    | BA     | В | (2)  | RxD  | В | DCE               | )       |

| 5      | A-C      | СВ     | A | (5)  | OPO  |   | DCE               | 1       |

|        | B - C    | CB     | A | (5)  | IPO  |   | DTE               | Channel |

| 6      | A-C      | CD     | A | (20) | OPO  |   | DTE               | A       |

|        | B - C    | CD     | A | (20) | IPO  |   | DCE               | )       |

| 7      | A-C      | СВ     | В | (5)  | OP1  |   | DCE               | 1       |

|        | B-C      | CB     | В | (5)  | IP1  |   | DTE               | Channe1 |

| 8      | A - C    | CD     | В | (20) | OP1  |   | DTE               | B       |

|        | B - C    | CD     | В | (20) | IP1  |   | DCE               | )       |

- 9 80186 Interrupt Output (Select VIO\*-VI6\* or VI7\*Parity error output)

- 10 Alternate S-100 port addresses

- 11 Alternate S-100 port addresses

Table 2: Switch Functions

| <u>s</u> | <u>Paddle</u> | Function                            |

|----------|---------------|-------------------------------------|

| 1        | 1             | Board Select Address Bit D3         |

|          | 2             | Board Select Address Bit D2         |

|          | 3             | Board Select Address Bit D1         |

|          | 4             | Board Select Address Bit DO         |

|          | 5             | Alternate S-100 I/O port addressing |

| 2        | 1-8           | Memory Address Bits A23-A16         |

### Switch Settings

Switch S1 uses paddle positions 1, 2, 3, 4, and 5. Switch S2 uses all of its paddles. The following is an overview and detailed description of each switch.

Switch 1 paddles 1 through 4 (S1-1 through S1-4) - 4-bit Select Address

The function of Switch 1 paddles 1, 2, 3, and 4 is to set the 4-bit select address of the board. Up to sixteen SP186 boards can be installed in a single system, with all their memory addressed at the same 64 Kbyte page in system memory and their two I/O ports overlapping. Each SP186 must have a different select address. To choose the board that you wish to communicate with, write its select address in the lower nibble to the SLVSEL port. You can now communicate with that board's memory and PORTL while the other SP186 boards are invisible. It is important always to start communication to a particular SP186 with a write of the correct select address to the SLVSEL port.

SP186 boards should be numbered starting with 0 and incremented with each additional board. For a system with one board, the settings should be:

BOARD 0 -- Paddles 1, 2, 3, and 4 ON

For a system with five SP186 boards, the settings should be:

BOARD 0 -- Paddles 1, 2, 3, 4 ON

BOARD 1 -- Paddles 1, 2, 3 ON, paddle 4 OFF

BOARD 2 -- Paddles 1, 2, 4 ON, paddles 3 OFF

BOARD 3 -- Paddles 1, 2 ON, paddles 3, 4 OFF

BOARD 4 -- Paddles 1, 3, 4 ON, paddle 2 OFF

If the SP186s in a system are configured for different I/O and memory addresses (through SI-5, J10, and J11), then the select address for all the boards can be the same. Normally, SI-1 through SI-4 of all the slaves are turned ON to give a select address of 0 for all the boards. In this way, the software can go to each board's SLVSEL port and write a 0. This allows all of the SP186's to have a memory window visible to the host at the same time. In this configuration, the software only has to write to each SP186 SLVSEL port once with a 0, and the boards will stay enabled and visible to the host until powered down.

Normally this approach is only practical in systems containing processors with large (>1 Mbyte) address spaces, such as a 32016-based system.

### S1-5 Alternate S-100 Port Address

S1-5 selects an S-100 I/O port address for the SP186. It is used in conjunction with J10 and J11. For a complete description of the use of this switch and what ports are selected, refer to the section on Jumpers J10 and J11, especially Table 3: I/O Port Selection.

## S2-1 through S2-8 Memory Address Bits A23-A16

Switch 2 determines where the 64 Kbyte page window of SP186 memory will appear to the system host and DMA devices. To CPU and DMA devices with 24 bits of addressing, the window appears in any one of 256 pages of memory. For CPU and DMA devices with 20 bits of addressing, the window is visible in any one of 16 pages. Paddle 1 is the most significant bit and corresponds with A23, while paddle 8 is the least significant bit and corresponds with A16.

The following are several examples of memory address selection:

| MEMORY | ADDRESS | S2 | Paddles |

|--------|---------|----|---------|

OFO000h to OFFFFFh -- 1,2,3,4 ON; 5,6,7,8 OFF. 450000h to 45FFFFh -- 1,3,4,5,7 ON; 2,6,8 OFF. A70000h to A7FFFFh -- 2,4,5 ON; 1,3,6,7,8 OFF.

## Jumper Settings

# J1 through J8 DCE or DTE Select

Jumpers J1 through J8 allow the SP186 channel A and channel B serial ports to respond independently as either DTE or DCE. They are shipped with normally closed connections that allow both ports to act as DTE and connect directly to DTE devices such as terminals. As long as both ports are connected to DTE devices, these jumpers don't need to be changed. If you want to connect a DCE-type device like a modem to the SP186, a serial port must be changed to look like DCE. This can be accomplished either by installing a "null modem" cable in the line between the SP186 and the DCE device, or by changing the appropriate jumpers on the SP186.

To change channel A to look like a DTE device, the small traces connecting J1 A-C, J2 B-C, J5 A-C, and J6 B-C must be cut on the solder side of the board. Pins should then be installed in J1, J2, and J6 with shunts placed across J1 B-C, J2 A-C, J5 B-C, and J6 A-C.

To change channel B to look like DTE, use the same procedure on J3, J4, J7, and J8. Under all circumstances, make sure that either channel is set completely for DTE or DCE according to the settings given above before applying power. For example, if J1 is set for DTE, J2 must be set for DTE.

CAUTION: If a channel has jumpers mixed, component failure can occur.

Jumpers J1 through J8 are 3-pin jumpers. Shunts are placed vertically across A-C (top 2 pins), or B-C (bottom 2 pins).

Jumpers J1, J3, J5, and J7 are shipped with a normally closed connection on the solder side of the board across A-C. Jumpers J2, J4, J6, and J8 are shipped with normally closed connections on the solder side of the board across B-C.

# J9 Vectored Interrupt Select

Jumper J9 controls which vectored interrupt (VI) lines the SP186 asserts. There are two conditions under which the SP186 can assert a VI line. The first is through the normal setting of an interrupt to the host when the 80186 writes to the SETINT100 port. The second is when the SP186 detects an on-board DRAM (Dynamic Random Access Memory) parity error.

Jumper J9 can be set to allow both conditions to assert the same vectored interrupt or different interrupts. Through two pin shunts that are placed horizontally across one of the eight positions, the SETINT100 interrupt can assert V10\* through V16\* and the parity error can assert V17\*. Refer to the physical diagram of the jumper below. A vertical shunt should be placed across the bottom two pins on the right side of the jumper to allow both conditions to assert the same VI line.

|    | VI line | <u>S100</u> pin | 78    | <u>SP186</u>                               |

|----|---------|-----------------|-------|--------------------------------------------|

|    | V10*    | <4>             | -o o- | - <interrupt output<="" td=""></interrupt> |

|    | VI1*    | <5>             | -o o  |                                            |

|    | VI2*    | <6>             | -0 0- | 4                                          |

|    | VI3*    | <7>             | -0 0- |                                            |

|    | V14*    | <8>             | -0 0- |                                            |

| 1  | V15*    | <9>             | -0 0  |                                            |

| 14 | V16*    | <10>            | -0 0- |                                            |

|    | VI7*    | <11>            | 0 0   | - Parity error output                      |

|    |         |                 |       |                                            |

### J10 and J11 S-100 Port Address Selection

Jumpers J10 and J11, in conjunction with S1-5, control which S-100 I/O port addresses the SP186s occupy. Depending on the particular software configuration, all the SP186s in a system can occupy the same two I/O ports and have overlapping memory banks, or each of them can have different I/O ports and appear in different 64 Kbyte memory pages.

If all of the SP186s are set for the same 1/O ports, then each must have a different select address chosen on Switch 1 paddles 1 through 4. In this way, up to sixteen SP186 boards can be in a single system, occupying only two I/O ports, and only one 64 Kbyte page of memory. This scheme is normally chosen when using 8088, 8086, or 80286 host processors due to their limited (1 Mbyte) memory addressing.

When using the 68000, 32016, or 80286 (protected) host processors with their expanded memory addressing (16 Mbytes), it is generally advantageous to give each SP186 a different set of I/O ports and 64 Kbyte memory page.

Up to eight different sets of I/O ports can be selected using J10, J11, and S1-5. It is also possible to have more than eight SP186 boards in a system at different I/O and memory locations. Please contact your Service Representative or CompuPro's technical assistance for information.

SP186 boards require two I/O ports; the SLVSEL port which is used to select one of the 16 boards, and the PORTL port which is used to control several functions of the currently selected board. The following table lists all possible locations for these two I/O ports.

Table 3: I/O Port Selection

| <u>S1-5</u> | <u>J11</u> | <u>J10</u> > | SLVSEL | PORTL  |

|-------------|------------|--------------|--------|--------|

| ON          | Removed    | Removed      | 0FC40h | 0FC41h |

| OFF         | Removed    | Removed      | OFG42h | OFC43h |

| ON          | Inserted   | Removed      | OFC44h | 0FC45h |

| OFF         | Inserted   | Removed      | OFC46h | 0FG47h |

| ON          | Removed    | Inserted     | OFC48h | 0FC49h |

| OFF         | Removed    | Inserted     | OFC4Ah | OFC4Bh |

| ON          | Inserted   | Inserted     | 0FC4Ch | 0FC4Dh |

| OFF         | Inserted   | Inserted     | OFC4Eh | 0FC4Fh |

|             |            |              |        |        |

In systems combining CompuPro SPUZ 8-bit Z80H based slave processors and SP186 16-bit 80186 based slaves, it may be desirable to overlap the I/O ports and 64 Kbyte memory page of the SP186 with the SPUZ. The SLVSEL port on both slaves makes this possible. On the SPUZ, the SLVSEL port is FC40h. Up to 16 slaves of either type can be in a system and use only one 64 Kbyte memory window by setting the SP186 SLVSEL port to 0FC40h, and the memory address of the SPUZ and SP186 to the same page.

Jumpers J10 and J11 are both 2-pin jumpers, with shunts that can either be inserted or removed.

# Theory of Operation

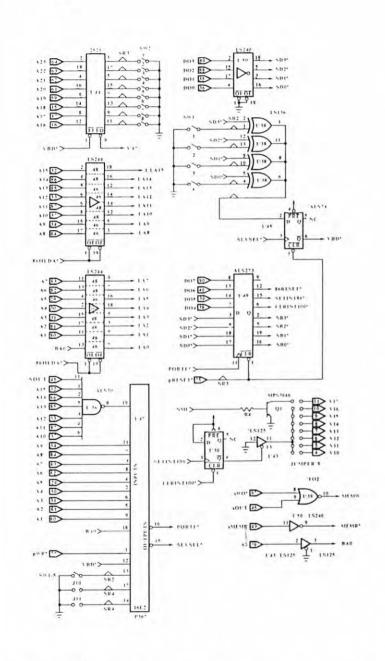

This section of the manual explains how the circuitry on the SP186 works. In the following discussions, it will be helpful to refer to the schematic diagrams.

### References

More detailed information about the 80186 MPU can be found in the 1985 Microsystems Components Handbook (order number 230843-002). Most of the information can be found in volume 1 of this 2 volume set. It can be obtained from Intel by contacting:

INTEL Literature Department 3065 Bowers Avenue Santa Clara, CA. 95051 (800) 538-1876, or (800) 672-1833 (CA only)

Part of Signetics' data sheet for the SC2681 Dual Asynchronous Receiver/Transmitter (DUART) is reprinted with permission in Appendix A.

The data sheet can be found in the Signetics MOS Microprocessor Data Manual for 1982 or later, and can be obtained by writing or calling Signetics at:

811 East Arques Avenue P.O. Box 409 Sunnyvale, CA. 94086 (408) 739-7700

### Overview

The SP186 appears as two I/O ports and 64 Kbytes of memory to the S-100 host processor or the temporary bus master (DMA device). Because it doesn't become a temporary master, it is restricted from accessing other user memory space or system peripherals.

The S-100 bus has full access to the SP186's 512 Kbytes of memory. An innovative structure allows the host processor to address the SP186's 64 Kbyte memory window on any 32 Kbyte boundary, thus reducing boundary checking by the host.

Another unique feature of the SP186 is its ability to allow two programs running on the SP186 to have separate interrupt vector tables, simplifying multi-tasking.

Inter-processor communication is accomplished through a bidirectional interrupt structure. Message passing is available through the memory located on the SP186. DMA devices can transfer data directly to or from the SP186's memory.

There is no EPROM on the SP186. When the system is powered up, the on-board 80186 stays reset until the S-100 host processor has put a program in the SP186's memory and allows the 80186 to run. The host processor can reset the SP186 at any time.

Parity checking on the SP186 RAM ensures data integrity.

The on-board dual UART is accessible to the 80186 and can handle speeds up to 38.4 Kbaud asynchronously. This allows the SP186 to be an effective front-end I/O pre-processor for use in OEM or custom systems where high speed or real-time processing of large quantities of data is necessary. Compiled data is passed to the host system for mass storage or further processing.

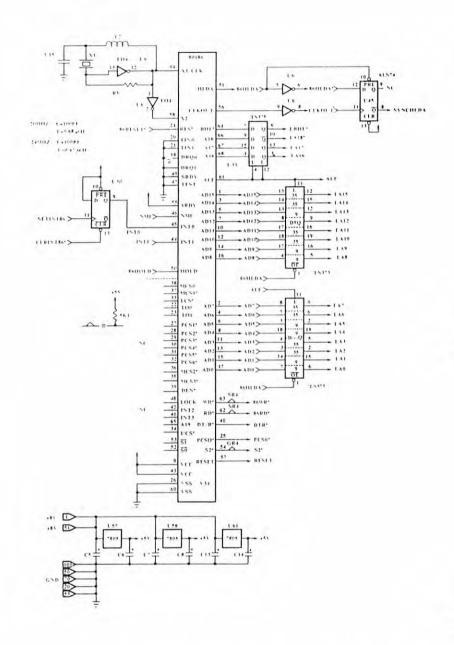

### Clock Generation

A 20 MHz clock is generated by two sections of inverter U6 (74F04), inductor L2, resistor R5, capacitor C15, and crystal X1. This clock is fed directly to the 80186, which divides it by 2 for its internal clock and generates the 80186's CLKOUT signal. CLKOUT is then inverted and used by flip-flop U45 (74ALS74) to generate SYNCHLDA\*. SYNCHLDA\* is the 86HLDA\* signal delayed by a portion of a clock width. The SYNCHLDA\* signal is used to start an external access to I/O or memory. This occurs after the S-100 addresses driven on to the internal bus by 86HLDA\* have settled.

### DRAM Refresh

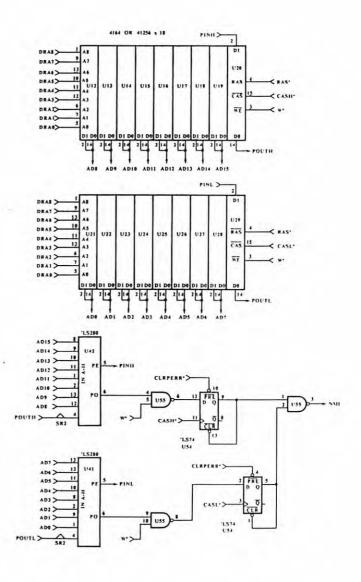

The 80186 does not require any memory wait states if at least 150 nanosecond DRAM is used. Refresh to the DRAM chips is provided by programming an 80186 DMA channel to read every location in memory sequentially at about 16 microsecond intervals between words. RAS\* is generated on every non-I/O cycle, regardless of address, allowing the DMA counter to scan through all of memory, refreshing it.

### The DUAKT Ports

The 2681 Dual Asynchronous Receiver/Transmitter (DUART) is I/O mapped into 32 ports of the 80186's I/O space through PCS0\* on the 80186. The base I/O port addresses can be selected in software. The 2681 is found only on the even Address/Data lines (AD0 through AD7 corresponding to ports 00h, 02h, 04h, 06h ... 01Eh) due to the SP186's 16-bit bus and the 2681's 8-bit bus. The ports listed in the 2681 data sheet should be doubled to get the actual port to the 80186. For example, to read 2681 port 06h (the CTU register), the 80186 must read port 0Ch. A description of the ports is contained in the reprint of the 2681 manual in Appendix A.

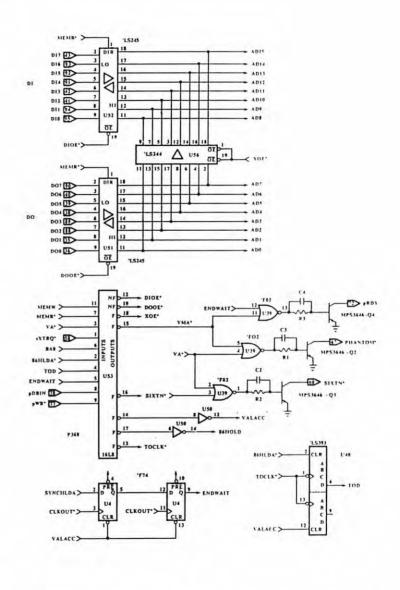

### S-100 Access to SP186 Memory

The data bus is buffered by U51 and/or U52 (74LS245) depending on whether it's an 8- or 16-bit transfer and in which direction the transfer is taking place. The SP186 conforms to the IEEE 696/S-100 specification for 8- and 16-bit transfers and will transfer a full 16 bits when requested.

DOOE\* and DIOE\* are asserted to the S-100 bus on host memory reads (sMEMR) when pDBIN and ENDWAIT are asserted and the proper status is met. On writes, DOOE\* and DIOE\* are asserted to the 80186 A/D bus when pWR\* and 86HLDA\* are asserted and the proper status is met.

Crossover buffering that conforms to the DI bus and DO bus 8-bit S-100 protocol is provided by buffer U56 (74LS244) either when the host is writing an odd byte or when it is reading an even byte. The S-100 address bus is buffered onto the internal address bus (LA bus) on 86HLDA\* by U46 and U48.

### SP186 Control Ports

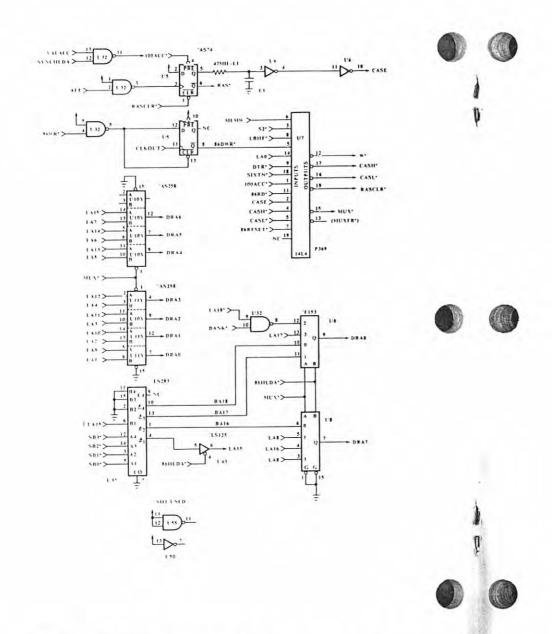

PAL U47 and NAND gate U36 (74ALS30) decode the S-100 I/O port addresses. The I/O addresses are decoded to produce PORTL\* and SLVSEL\* depending on the state of pins 13, 14, and 17 of PAL U47. SLVSEL\* is produced regardless of the state of VBD\*. This allows the compare circuitry, composed of U38 (74LS136) and flip-flop U45 (74ALS74), to select one of 16 slaves with a single I/O write when all of their SLVSEL\* ports overlap. When VBD\* is asserted low, VA\* is asserted, enabling a memory cycle, and PORTL\* is asserted,

writing control information to U49 (74ALS273). If all of the SP186s in a system have different SLVSEL\* addresses, a single write to each board's SLVSEL\* port with the correct select address will enable the board, turning on VBD\*. Only if RESET\* is asserted or SLVSEL\* is written again with an incorrect select address will VBD\* be negated, de-selecting the board.

The port map is shown following.

## Table 4: SP186 Port Map

Port Function

Low SLVSEL\* - Selects which board within a bank of 16 is selected. (Write Only)

High PORTL\* - Controls 86RESET\*, interrupt handshaking lines, and DRAM address for S-100 bus accesses.

(Write Only)

The low port can be 0FC40h, 0FC42h, ..., and the high port can be 0FC41h, 0FC43h, ..., depending on the setting of J10, J11, and S1-5 (refer to the previous section on Jumpers J10 and J11). In systems with overlapping I/O ports, SLVSEL\* is asserted on all the boards in the system, while PORTL\* is asserted only on the board that has been selected by SLVSEL\*. In systems with non-overlapping I/O ports, the proper select address must be written to each board separately through SLVSEL\*, because PORTL\* and memory accesses are not allowed until the board is selected.

When the extended address (A16-A23) matches what is set on Switch 2 and the signal VBD\* is asserted, comparator U44 (25LS2521) asserts VA\*. The system can access the SP186's internal memory when VA\* is low, when pDBIN or pWR\* is asserted, and when the proper status is met on sMEMR, sWO\*, and sOUT. Thus, to access a memory location on the SP186 (when it is running, not reset), first write the proper data pattern to the SLVSEL\* to clock in VBD\* on the trailing edge of pWR\*, then access the 64 Kbyte SP186 memory window.

The 8-bit write only port PORTL\* is composed of U49 (74ALS273). Only the host can write to this port.

The bit map is as follows. The values given in parentheses are how the board comes up after a RESET\* to the system.

### Table 5: PORTL\* Bit Map

| Bit | Name       | Function                                                                                                                                                     |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | ne         | Isn't used; output isn't connected.                                                                                                                          |

| D6  | 86RESET*   | Write a 0 to reset the 80186.<br>Write a 1 to allow 80186 to run.<br>(0 - 86RESET* asserted low).                                                            |

| D5  | SETINT86   | Write a 0 then a 1 to cause an interrupt to the 80186. Rising edge triggered. (0 - ready to cause interrupt by writing 1).                                   |

| D4  | CLRINT100* | Write a 0 to clear the VI from the 80186. Write a 1 to enable the VI from the 80186. (0 - interrupt cleared).                                                |

| D3  | SB3*       | Controls which memory the S-100                                                                                                                              |

| D2  | SB2*       | host accesses. These 4 bits control                                                                                                                          |

| D1  | SB1*       | which of the sixteen 64 Kbyte pages                                                                                                                          |

| D1  | SB0*       | in 512K DRAM (32 Kbyte boundaries) is selected. (0000b - comes up pointing to bottom memory.                                                                 |

|     |            | NOTE: These last 4 bits are inverted coming off the S-100 bus. That is, to access the bottom 64 Kbytes, the software must write a 1111b to the lower 4 bits. |

### SP186 Initialization

The initialization of the SP186 is critical. If the host accesses the SP186 memory when the 80186 is reset, the S-100 system crashes. The reason for this is that the host's access to the SP186 memory must be arbitrated by the 80186; if the 80186 is reset when memory is requested, the 80186 never issues an 86HLDA\* allowing the cycle to take place. When the SP186 asserts pRDY to wait for the 80186 to give an 86HLDA\*, the S-100 system hangs forever in a wait state.

To avoid this situation, when loading the SP186 memory, first allow the 80186 to run, load a small amount of code at the 80186's boot address 0FFFF0h, reset the 80186, wait, and allow the 80186 to run again. Check to make sure the code is intact and was not corrupted when the 80186 was running random code. Remember that the DRAM is not being refreshed except at the locations where the 80186 is running; the host must take this responsibility until the 80186 can be programmed to do it itself.

A programming example of how to do this is described in the software section and shown in Appendix B.

### 80186 Reset

The 86RESET\* bit is set high to allow the 80186 to run. To reset the 80186 and 2681, set this bit low. This bit is set low on RESET\* from the S-100 bus. The interrupt latches, consisting of both parts of U30 (74LS74), constitute a bidirectional interrupt structure. On RESET\* from the S-100, the interrupt from the SP186 is cleared by CLRINT100\*. No interrupt (VI) can be asserted, regardless of what the 80186 does, until the CLRINT100\* bit is set high.

### Interrupts

When CLRINT100\* is set high, the 80186 can cause a VI with a rising edge of SETINT100 by first setting OP2 on the 2681 (U31) low and then setting it high (write a 1 and then a 0 to D2 of OPR). The host then clears the interrupt by lowering CLRINT100\*.

NOTE: As long as CLRINT100\* is low the 80186 cannot set an interrupt pending. Care must be taken to ensure that the 80186 never tries to SETINT100 while CLRINT100\* is low, as the host does not get the interrupt, and the SETINT100 transition is lost.

A very similar setup forms the interrupt input to the 80186. Lowering the CLRINT86\* bit by programming OP3 of the 2681 low clears the interrupt to the 80186. When CLRINT86\* is high, a rising edge on the SETINT86 (first write a 0, then a 1 to bit D5 in PORTL) causes the INTO line into the 80186 to be asserted. INTO can then be negated by the 80186 by setting the CLRINT86\* bit low. The same constraints on CLRINT100\* and SETINT100 are present on CLRINT86\* and SETINT86. If CLRINT86\* is asserted low, no transitions on SETINT86 can cause an interrupt, and those transitions will be lost.

Memory Addressing on a 32 Kbyte Boundary by Host Processor

To climinate the constant need for the host to check page boundaries when reading or writing to slave memory, adder U37 (74LS283) was included on the board to allow the internal DRAM 64 Kbyte window to be addressed at any 32 Kbyte boundary. By setting the SB(x)\* bits correctly, the host is guaranteed a contiguous 32 Kbyte region (inside the 64 Kbyte external window), without having to worry about crossing over 64 Kbyte boundaries.

For example, to write 2 Kbytes to location 0FF00h in memory using traditional mapping schemes, you would first set the window to page 0 (see DRAM between 00h and 0FFFFh), then write 0100h bytes out of the 2 Kbytes to 0FF00h through 0FFFFh. Next, set the window page to 1 (see DRAM between 010000h and 01FFFFh), and write the remainder to 010000h through 0106FFh.

Using the SP186's 32 Kbyte windows, simply set the window to 08000h (see DRAM between 08000h and 017FFFh), and write the 2K block in one operation. This is particularly critical when using a DMA device to load the SP186 directly.

To set the internal window to 0 (see DRAM between 00h and 0FFFFh), write a 01111h to the SB(x)\* bits in the PORTL\* port. To set the window to 08000h (see DRAM between 08000h and 017FFFh), write a 01110h to the SB(x)\* bits.

The following table shows which DRAM address on the SP186 is visible to the host within the 64-Kbyte window by setting the SB(x)\* bits.

Table 6: DRAM Addressing

| <u>SB3*</u> | SB2* | <u>SB1*</u> | <u>SB0*</u> | DRAM on | 51 | 2K board |  |

|-------------|------|-------------|-------------|---------|----|----------|--|

| 1           | 1    | 1           | 1           | 00h     | to | OFFFFh   |  |

| 1           | 1    | 1           | 0           |         |    | 017FFFh  |  |

| 1           | 1    | 0           | 1           |         |    | 01FFFFh  |  |

| 1           | 1    | 0           | 0           |         |    | 027FFFh  |  |

| 1           | 0    | 1           | 1           |         |    | 02FFFFh  |  |

|             |      |             |             |         |    |          |  |

|             |      |             |             |         |    |          |  |

|             |      |             |             |         |    |          |  |

| 0           | 0    | 1           | 0           | 068000h | to | 077FFFh  |  |

| 0           | 0    | 0           | 1           | 070000h |    |          |  |

| 0           | 0    | 0           | 0           | 078000h |    |          |  |

|             |      |             |             |         |    |          |  |

Example: Write a 055h to location 013200h. The 64 Kbyte window on the host is from 0F0000h to 0FFFFFh (S2 = 0Fh).

Host enables the board with a write to the SLVSEL port. Host writes a 01101h to the SBx\* bits of the PORTL port. Host writes the 055h to 0F3200h to complete transaction.

Care must be taken when DMA devices with real-time requirements access the SP186, because the 80186 isn't guaranteed to give up its internal bus in any specified amount of time. Furthermore, it will lock out the bus for several microseconds every eight consecutive accesses in order to run a refresh cycle. This ensures that no host software manipulations will cause a loss of refresh on the SP186.

# The DUART Input and Output Bits

The 2681 DUART handles:

- The serial receive/transmit function

- · Several output bits necessary on the board

- · Several input bits

- The timer/counter.

The 2861 can assert the INT1 interrupt on the 80186 using its INTRN output. The 16 ports of the DUART control these functions and are defined in the reprint of the 2681 Data sheet in Appendix A.

The output bits of the 2681 are defined in the following table. All the bits in the OPR are low on reset, and the remarks in parentheses explain what this means to the circuitry.

Table 7: Output Bits of the 2681

| <u>Bit</u> | Function  | Description                                                                                                                                                                                                                                                |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP7        | CLRPERR   | Enables and Disables DRAM parity checking. (Parity checking disabled on RESET*)                                                                                                                                                                            |

| OP6        | BANK*     | Enables SP186s to swap the upper 256 Kbytes of memory with the lower. (Normal linear mapping on RESET*)                                                                                                                                                    |

| OP5        | nc        |                                                                                                                                                                                                                                                            |

| OP4        | nc        |                                                                                                                                                                                                                                                            |

| OP3        | CLRINT86* | Asserts CLR to the flip-flop<br>that controls INTO to the<br>80186. (Allows INTO to be<br>asserted; INTO could be<br>asserted at power-on)                                                                                                                 |

| OP2        | SETINT100 | Provides the transition to cause a Vectored Interrupt to S-100 bus. (Initially high; needs to be set low, then high to cause interrupt)                                                                                                                    |

| OP1        | RTS out B | Request to Send output B. If<br>the SP186 is set to be DCE as<br>shipped, this bit goes to RS-<br>232 CTS pin 5 for channel B.<br>If the SP186 is DTE, then this<br>bit provides DTR pin 20.<br>(Forces DTR or CTS to spacing,<br>inhibiting transmission) |

| OPO        | RTS out A | Request to Send output A. If<br>the SP186 is set to be DCE as<br>shipped, this bit goes to RS-<br>232 CTS pin 5 for channel A.<br>If the SP186 is DTE, then this<br>bit provides DTR pin 20.<br>(Forces DTR or CTS to spacing,<br>inhibiting transmission) |

The following table defines the input bits of the 2681:

Table 8: Input Bits of the 2681

| Bit | Function | Description                                                                                                                                                                              |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP6 | nc       |                                                                                                                                                                                          |

| IP5 | nc       |                                                                                                                                                                                          |

| IP4 | nc       |                                                                                                                                                                                          |

| IP3 | DCD in B | Data Carrier Detect input B. This bit comes from the RS-232 Carrier Detect pin 8 channel B. This bit is normally only used when the SP186 is DTE.                                        |

| IP2 | DCD in A | Data Carrier Detect input A. This bit comes from the RS-232 Carrier Detect pin 8 channel A. This bit is normally only used when the SP186 is DTE.                                        |

| IP1 | CTS in B | Clear to Send input B. If the SP186 is set to be DCE as shipped, the bit comes from RS-232 DTR pin 20 for channel B. If the SP186 is DTE, this bit monitors the CTS pin 5 for channel B. |

| IPO | CTS in A | Clear to Send input A. If the SP186 is set to be DCE as shipped, the bit comes from RS-232 DTR pin 20 for channel A. If the SP186 is DTE, this bit monitors the CTS pin 5 for channel A. |

## DRAM Parity Checking

DRAM parity generation and checking is done in U41 and U42 (74LS280) and latched in U54 (74LS74). When a parity error is detected on the SP186, NMI\* (non-maskable interrupt) is sent to the 80186 or an S-100 Vectored Interrupt can be asserted. Normally, this type of error causes the host to abort the processes in the particular slave due to potentially unreliable results within the slave memory. A memory check is then run to make sure that the error is soft (e.g., alpha particle), and new processes are loaded. When the system is RESET\*, parity is disabled. If parity checking is not desired on the board, no action is necessary except to make sure that bit 7 in the 2681 OPR is never set.

To activate parity, the software must first initialize the parity check DRAM chips U20 and U29 by writing to every location. A loop that reads each location (wordwide, from 0h to 0FFFEh) and writes the same location back is effective in initializing the DRAM. Not until every byte has been initialized (written) can parity be activated. Set D7 in the 2681 OPR high to allow parity checking to start. Parity will be checked on every 80186 memory read (including opcode fetches) and on reads of DRAM from the host. Parity is generated on every write to the DRAM, whether from the 80186 or from the host system.

### Multi-tasking

A unique banking feature allows the SP186 to swap the upper and lower 256 Kbyte bank in its memory map. This allows two processes, one running in the physically lower memory and one in the physically higher memory to think that they are both executing in lower memory with their own interrupt vector table. To conceptualize this, think of the total 1 Mbyte address range of the 80186 as four 256K regions, labeled A0, A1, A2, and A3. Next, think of the 512 Kbytes of physical memory as two 256 Kbyte regions, labeled M0 and M1. On 86RESET\* bit 6 in the 2681 OPR is set low, negating BANK\*. This results in the following memory map:

Table 9: 80186 Memory Map with BANK\* Negated

| 80186 Memory        | > | Phy | sical | Memory |

|---------------------|---|-----|-------|--------|

| AO (OOh to O3FFFFh  | ) | мо  | (bank | 0)     |

| Al (040000h to 07F  |   | M1  | (bank | 1)     |

| A2 (080000h to 0BF  |   | MO  | (bank | 0)     |

| A3 (0C00000h to 0FF |   | M1  | (bank | 1)     |

NOTE: The 512 Kbyte memory appears in both the upper and lower halves of the 1 Mbyte range of the 80186 address space. This allows the 80186 DMA channel to refresh the 512 Kbytes even though it's scanning through all of the 1-Mbyte space. Memory also appears at the 80186's boot location 0FFFF0h without having to put separate memory there.

By setting bit 6 in the 2681 OPR, BANK\* is asserted. This changes the memory map to the following:

Table 10: 80186 Memory Map with BANK\* Asserted

| 80186 Memory>         | Physical Memory |

|-----------------------|-----------------|

| AO (Oh to 3FFFFh)     | M1 (bank 1)     |

| A1 (40000h to 7FFFFh) | M1 (bank 1)     |

| A2 (80000h to BFFFFh) | M1 (bank 1)     |

| A3 (C0000h to FFFFFh) | M1 (bank 1)     |

Physical memory bank 0 disappears and physical memory bank 1 appears in every 256 Kbyte 80186 memory bank. Refresh by the 80186 DMA controller continues to function properly.

### Dual Ported Memory Arbitration

S-100 bus access to the resources of the SP186 is controlled by PAL U53 (part p368). It controls the necessary status and strobes to run an internal bus cycle. The PAL generates pRDY when the proper status is met, and does not end pRDY until ENDWAIT is generated by counter U4. PAL U53 also controls the assertion of PHANTOM\* and SIXTN\*, thus allowing the SP186 to overlap system memory and to respond and transfer a full 16 bits at a time. The chain of events for a single memory transfer is:

- Host or DMA device requests memory (correct status and address).

- SP186 puts host of DMA device in wait state and asserts 86HOLD to the 80186.

- 80186 issues 86HLDA\*, which puts data (on write) and address on the internal bus.

- SYNCHLDA\* is asserted, which starts counter U4, and causes a RAS\* to start through U32 (74F00) and U5 (74AS74).

- 5. DRAM read or write cycle is performed depending on MEMW.

- ENDWAIT is asserted, which terminates pRDY and drives data onto the S-100 bus for a read.

Half of counter U40 (74LS393) controls the hold off, which keeps the 80186 in hold by asserting 86HLDA\* for a certain number of strobes after the last access. This counter also ensures that the host does not keep the 80186 in hold too long. If this happened, refresh of the DRAM could be lost. Therefore, the host or DMA device can't run more than eight cycles on the internal bus before the SP186 forces the host or DMA device to wait and run a cycle of its own. Refresh is maintained in this way.

### SP186 Internal Timing

The 2681 interface is straightforward. When the 80186 asserts PCS0\* and either 86WR\* or 86RD\*, the 2681 either accepts data or presents data to the bus AD7 through AD0. The address LA4-LA1 controls which section of the 2681 is accessed. Since the 80186 has a 16-bit bus and the 2681 has an 8-bit bus, all ports accessing the 2681 are even, and double what is shown in the 2681 manual (shifted to the left one bit). The 16 ports of the 2681 then appear at 00h, 02h, 04h, ... 01Ch, 01Eh.

The port map for the 2681 is in the reprint of its data sheet. The time base for the 2681's baud-rate generator and counter timer is the 3.6864 MHz crystal X2. The 2681 is reset whenever the 80186 is reset as the 80186 RESET\* output goes to the 2681. The INTRN output is able to assert INT1 to the 80186 through inverter U1.

The Dynamic RAM circuitry provides liberal timing to the RAM chips, while maintaining high speed.

- ALE's trailing (falling) edge provides the clock to U5.

This starts the DRAM cycle because all addresses are valid at that edge.

- The delay introduced by L1 and C1 provides the RAS/address hold time, and U6 and PAL U7 provide the address/CAS setup time after the addresses have been multiplexed through U10, U11, and U8.

- On 80186 accesses, CAS is delayed until either 86RD\* or 86DWR\* is asserted.

- On a read, CAS is held until the trailing edge of 86RD\*, so that data is properly latched into the 80186.

- On a write, data flows from the data lines into the DRAM when 86DWR\* is asserted, and RAS and CAS are held until the end of 86DWR\*.

When setting up the internal DMA counter and timer to cause a refresh, make sure that 256 consecutive words are refreshed over a total time of no more than every 4 milliseconds. If evenly spaced, this gives about 15 microseconds between word refreshes.

# Programming for the SP186

### Introduction

If you are running the SP186 under a CompuPro operating system, refer to the System Installation Guide for standard switch and jumper settings and for installation of the software to run 16-bit programs on the 186 slave.

If you are trying to bring up the SP186 in some other environment, study the code in Appendix B before you write any of your own code. Appendix B is a sample CP/M 86 program that loads some initialization code into the 80186 and starts it executing. No representation is made that this is the best way to program the SP186; it simply illuminates some of the possible pitfalls in getting the SP186 up and running.

The values loaded by the sample program into the internal registers of the 80186 and the 2681 DUART are typical values only, and may not be applicable to every system. Please consult the data sheet for the 80186 MPU and 2681 DUART if custom programming for the SP186 is done.

### SP186 Hardware Initialization

The SP186 is designed so that up to 16 SP186 boards can all reside in the same 64K memory page and use the same two I/O ports. The S-100 host CPU must choose which SP186 it wants to talk to. If there is only one, it should have a select address of 00h, and thus the system should write a 00h to the select port (SELsp86 in the sample listing). The select value can be between 00h and 0Fh depending on which one of up to 16 SP186 boards you want to access. Even if the SP186 is the only board that resides in a particular memory page and I/O port, it must still be selected before the host CPU can access it.

When the board is powered up, the 80186 is in a reset state and it can not arbitrate for it's internal bus with the host processor. Any access to the SP186's memory would cause the S-100 bus to hang forever in a wait state, waiting for the 80186 to give the host processor the internal bus. It is imperative that the 80186 not be in a reset state when the host attempts to access the SP186 internal DRAM. Writing a 041h to the SP186 information port (INFsp86 in the sample listing) releases reset to the 80186, and sets external host window to the top 64K page of internal DRAM.

The 8016 is now running whatever random code happens to be at 0FFFF0h (the 80186 restart vector). The host CPU should then move a HALT instruction (opcode 0F4h) to location 0FFFF0h of the 80186, and then issue a reset back to the 80186.

After waiting to make sure that the 80186 gets reset in even the fastest systems (1 uSec is enough), let the 80186 run again, at which time it should pick up the 0F4h opcode and enter a HALT state. It is important for the host CPU to check that the 0F4h is still there, as it could possibly have been corrupted by the 80186 itself when the 80186 was running the arbitrary code. If 0F4h is not found, the process should be repeated until it is, guaranteeing the 80186 is now in a known state.

### Refresh

Once the 80186 is in a HALT, the host can safely load code into the 80186 DRAM, including the code that initializes the DUART, the internal 80186 port map, and the code that causes the DMA counters to refresh (it should cause a refresh of a word at least every 15 microseconds). It is important that during this time the host maintains refresh on the DRAM by accessing any consecutive 256 words at least once every 4 milliseconds. Simply loading code to at least 256 words in a row can provide this refresh.

### 80186 Sample Listing

The sample loader in Appendix B initializes the 80186 as above by writing a 0 to the select port and calling a subroutine called "START\_REFRESH".

The START REFRESH routine first puts the 80186 in a halt and verifies that it got in a halt by checking that the HALT opcode is intact at location 0F000:FFF0H. It then loads the code at the label "DDRAM" to location 0F000:F000 in the 80186 memory map. The DDRAM code initializes the internal ports and DMA channels so that DMA channel 0 and TIMER 2 can take care of refreshing the DRAM.

A far jump is then put at the 80186 restart vector (0F000:FFF0H) and the reset line is raised and lowered, causing the 80186 to execute the initialization code. The host processor will then wait for the 80186 to change the byte at F000:FFF0h to 0, signaling that the 80186 finished executing the initialization code. Once the 80186 has set

the flag to 0, signaling that it is finished with the initialization code, it reads that byte. When the 80186 reads 0FFh, it jumps to the location pointed to at 0F000:FFF1h.

The host processor finally loads the runtime code SP186 \_ CODE (this would normally be whatever runtime code was to be executed) to 40:80h in the SP186 RAM, fills in the jump vector, and signals the 80186 to execute.

The 80186 jumps to 40:80h, the routine to set up the 80186 interrupt vectors, initialize the 2681 DUART and the 80186 interrupt controller, and print a message to a terminal hooked up to channel A at 19.2k baud. The 80186 then sits in a simple idle loop.

The HOST and DUART interrupt vectors are set to go to routines that will print a message to the terminal on channel A, send the 80186 EOI and return. All of the rest of the interrupts are set to go to a trap routine that will print the offending interrupt number on the terminal on channel A.

1 of 6

AD6> ADS> RXD ADA ADI> ADI> ADOS CARRIET CO CEN LAIS OPI XI/CLK 3.4844MHZ 3.1 CARRIER DETECT 2681 UJI 16 SRI 13 SRI 13 SRI 18 SRI 39 37 27 14 - CLRINTS4" - SETINTING OP4 INTRN NORMALLY CLOSED CONNECTION (AC) TO CONNECT DIRECTLY TO TERMINAL (DTE), FIGURE I. +12V (TO 1488) OPPOSITE CONNECTION (BC) TO CONNECT TO MODEN (DCE). FIGURE 1 SPIRA-DTE - - 12V (TO 1411) TOP VIEW - TOP OF BOARD 34 PIN SHROUDED

3 of 6

SP186 366A1 Viasyn Corporation o 1986

4 of 6

SP186 366A1 Viasyn Corporation © 1986

SP186 366A1 Viasyn Corporation c 1986

5 of 6

SP186 366A1 Viasyn Corporation c 1986

# Parts List

| Name      | CompuPro PN    | Quantity | Location           |

|-----------|----------------|----------|--------------------|

| Integrate | d Circuits     |          |                    |

| 74F00     | 3160-0000      | 1        | U32                |

| 74LS00    | 3140-0000      | 1        | U55                |

| 74F04     | 3160-0004      | 1        | U6                 |

| 74F02     | 3160-0002      | 1        | U39                |

| 74ALS30   | 3150-0030      | 1        | U36                |

| 74LS74    | 3140-0074      | 3        | U4,U30,U54         |

| 74AS74    | 3145-0074      | 1        | U5                 |

| 74ALS74   | 3150-0074      | 1        | U45                |

| 74LS125   | 3140-0125      | 1        | U43                |

| 74LS136   | 3140-0136      | 1        | U38                |

| 74F153    | 3160-0153      | 1        | U8                 |

| 74AS258   | 3145-0258      | 2        | U10,U11            |

| 74LS240   | 3140-0240      | 1        | U50                |

| 74LS244   | 3140-0244      | 3        | U46,U48,U56        |

| 74LS245   | 3140-0245      | 2        | U51,U52            |

| 74ALS273  | 3150-0273      | 1        | U49                |

| 74LS280   | 31,40-0280     | 2        | U41,U42            |

| 74LS283   | 3140-0283      | 1        | U37                |

| 74LS373   | 3140-0373      | 2        | U9,U35             |

| 74LS375   | 3140-0375      | 1        | U33                |

| 74LS393   | 3140-0393      | 1        | U40                |

| 25LS2521  | 3140-1000      | 1        | U44                |

| 1488      | 3186-0000      | 1        | U2                 |

| 1489      | 3186-0010      | 2        | U1,U3              |

| 7805      | 319,7-0020     | 3        | U57,U58,U61        |

| 78L12     | 3197-0060      | 1        | U59                |

| 79L12     | 3197,0070      | 1        | U60                |

| 80186     | 3190-0025      | 1        | U34                |

| 16L8      | 3135-0050      | 1        | U53                |

| 16L2      | 3135-0040      | .1       | U47                |

| 14L4      | 3135-0020      | 1        | U7                 |

| 4164/256  | 3172-4164/0000 | 18       | U12-U29            |

| 2681      | 3186-2681      | 1        | U31                |

| Transisto | ors            |          |                    |

| MPS3646   | 4850-0040      | 4        | Q1,Q2,Q3,Q4        |

| Resistors |                |          |                    |

| 5.1KSIP   | 4730-0210      | 4        | SR1, SR2, SR3, SR4 |

| 1K5       | 4710-0460      | 3        | R1,R2,R3           |

| 2K2       | 4710-0480      | 1        | R4                 |

| 1K0       | 4710-0440      | 1        | R5                 |

This page intentionally blank

| NAME     | CompuPro PN     | Quantity | Location     |

|----------|-----------------|----------|--------------|

| Capacito | ors             |          | 34           |

| Ceramic  | Bypass          | 27       | all unmarked |

| Radial ' | TANTALUM        | 10       | C5-C14       |

| 47pF ce  | r 1550-0010     | 3        | C2, C3, C4   |

| 100pFmi  | ca 1530-0100    | 2        | C1,C15       |

| Inducto  | rs              |          | 2.2          |

| 1.OuH    | 1810-0009       | 1        | L2           |

| 10uH     | 1810-0016       | 1        | L1           |

| Crystal  | S               |          |              |

| 3.6864   | MHz Fundamental | 1        | X2           |

| 20 MHz   |                 | 1        | X1           |

| Miscell  | aneous          |          |              |

| TANDEM   | DIPSHUNT        | 1        | FOR J9       |

| 8-POS D  | IPSWITCH        | 2        | S1,S2        |

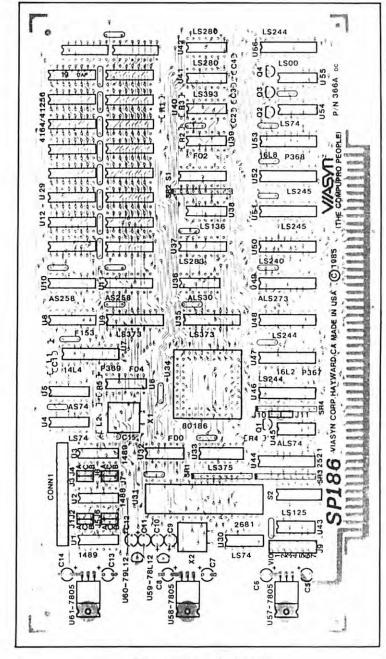

Component Layout

# Appendix A The DUART

MICROPROCESSOR DIVISION

### DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER (DUART)

### SC2681 SERIES

#### DESCRIPTION

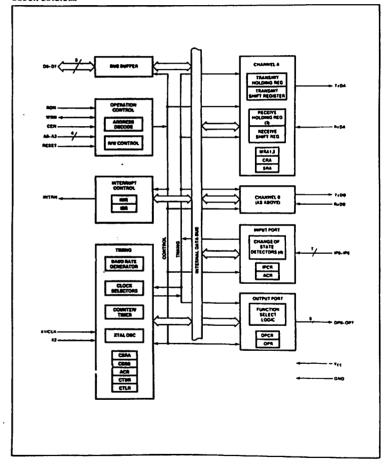

The Signetics SC2681 Dual Universal Asynchronous Receiver/Transmitter (DUART) is a single chip MOS-LSI communications device that provides two independent fullduplex asynchronous receiver/transmitter channels in a single package. It interfaces directly with microprocessors and may be used in a polled or interrupt driven sys-

The operating mode and data format of each channel can be programmed independently Additionally, each receiver and transmitter can select its operating speed as one of eighteen fixed baud rates, a 15x clock derived from a program counter/timer, or an external 1x or 16x clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the DUART particularly attrac tive for dual-speed channel applications such as clustered terminal systems

Each receiver is quadruply buffered to minimize the notential of receiver overrun or to reduce interrupt overhead in interrupt driven systems. In addition, a flow control capability is provided to disable a remote DUART transmitter when the bulfer of the receiving device is full.

Also provided on the SC2681 are a multipurpose 7-bit input port and a multipurpose 8-bit output port. These can be used as general purpose I/O ports or can be assigned specific functions (such as clock innuts or status/interrupt outputs) under program control

The SC2661 is available in three package versions to satisfy various system requirements 40 pin and 28-pin, both 0.6" wide DtPs, and a compact 24-pin, 04" wide,

#### **FEATURES**

- Duel full-duples asynchronous receiver

- Quadruple buffered receiver data regie

- -5 to 6 data bits plus parity

- -Odd, even, no parity or force parity -1, 1.5 or 2 stop bits programmable in

- Programmable baud rate for each receiver and transmitter selectable from: - 18 fixed rates: 50 to 38.4K baud

- -One user defined rate derived from

- Faternal 1s or 18s clock Parity, framing, and overrun error detec-

- Fates start bit detection

- Line break detection and generation

- Normal (full duples)

- -Automatic echo

- Remote locoback

- Multi-function programmable 18-bit

- Mutti-function 7-bit input port -Can serve as clock or control inputs

- -Change of state detection on four

- Mutti-function 8-bit output port dividual bit settreest capability

- -Outputs can be programmed to be status/interrupt signals

- Versetile interrupt system -Single interrupt output with eight maskable interrupting conditions

- -Output port can be configured to provide a total of up to six separate wire-OR'able Interrupt outputs

- Maximum data transfer: 1X 1M8/sec, 16X - 125KB/sec

- · Automatic wake-up mode for multidrop

- . Start-end breek interrupt/status

- . Detects break which originates in the

- middle of a characte · On-chip crystal oscillator

- TTL compatible

- . Single + 5V power supply

### ORDERING CODE

| PACKAGES 24 Pln <sup>1</sup> Ceramic DIP SC2681CS124 | y ± 5%, T <sub>A</sub> = 0°C to 70°C |                            |                            |  |

|------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|--|

| PACKAGES                                             | 24 Pin <sup>1</sup>                  | 28 Pin <sup>3</sup>        | 40 Pin²                    |  |

| Ceramic DIP<br>Pleatic DIP                           |                                      | SC2681CS128<br>SC2681CSN28 | SC2681CS140<br>SC2681CSN40 |  |

2000 me ando Del

#### PIN CONFIGURATION

o' 🖽

lm ⊶

#### MICROPROCESSOR DIVISION

### **DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER (DUART)**

SC2681 SERIES

### Permer

#### **BLOCK DIAGRAM**

# DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER (DUART) SC2681 SERIES

#### Preview

#### PIN DESIGNATION

| 10.75.707.2 | APP | LICA | BLE | -    | NAME AND FUNCTION                                                                                                                                                                                                                                       |  |  |  |

|-------------|-----|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MNEMONIC    | 40  | 28   | 24  | TYPE |                                                                                                                                                                                                                                                         |  |  |  |

| D0-D7       | ×   | ×    | ×   | 1/0  | Data Bus; Bidirectional 3-state data bus used to transfer commands, data and status between the DUART and the CPU. DO is the least significant bit.                                                                                                     |  |  |  |

| CEN         | x   | x    | x   | T    | Chip Enable: Active low input signal. When low, data transfers between the CPU and the<br>DUART are enabled on D9-D7 as controlled by the WRN, RDN and A0-A3 inputs. When high,<br>places the D9-D7 lines in the 3-state condition.                     |  |  |  |

| WRN         | ×   | x    | ×   | V.   | Write Strobe: When low and CEN is also low, the contents of the data bus is loaded into the addressed register. The transfer occurs on the rising edge of the signal.                                                                                   |  |  |  |

| RDN         | x   | ×    | ×   | 1    | Read Strobe: When low and CEN is also low, causes the contents of the addressed register to be presented on the data bus. The read cycle begins on the falling edge of RDN                                                                              |  |  |  |

| A0-A3       | ×   | ×    | ×   | 1    | Address Inputs: Select the DUART internal registers and ports for read/write operations                                                                                                                                                                 |  |  |  |

| RESET       | x   | x    | ×   | t    | Reset: A high level clears internal registers (SRA, SRB, IMR, ISR, OPP, OPCR), puts OPO-OP7 in the high state, stops the counter/timer, and puts channels A and B in the inactive state, with the TsDA and TsDB outputs in the mark (high) state.       |  |  |  |

| INTRN       | ×   | x    | ×   | 0    | Interrupt Request: Active low, open drain, output which signals the CPU that one or more of the eight maskable interrupting conditions are true.                                                                                                        |  |  |  |

| X1/CLK      | x   | x    | x   | 1    | Crystal 1; Crystal or external clock input. A crystal or clock of the specified limits must be supplied at all times.                                                                                                                                   |  |  |  |

| X2          | ×   | *    | 1   | 1    | Crystal 2: Connection for other side of the crystal. Should be open if crystal is not used                                                                                                                                                              |  |  |  |

| REDA        | ×   | ×    | ×   | T    | Channel A Receiver Serial Data Input: The least eignificant bit is received first. 'Mark' is high 'space' is low.                                                                                                                                       |  |  |  |

| RxDB        | ×   | ×    | ×   | 4    | Channel B Receiver Serial Data Input: The least significant bit is received first. 'Mark' is high 'space' is low.                                                                                                                                       |  |  |  |

| Taba        | ×   | x    | ×   | 0    | Channel A Transmitter Serial Data Output: The least significant bit is transmitted first. This output is held in the "mark" condition when the transmitter is disabled, idle, or when operating in local loopback mode. "Mark" is high, "space" is low. |  |  |  |

| TxDB        | x   | ¥    | ×   | 0    | Channel B Transmitter Serial Data Output: The least significant bit is transmitted first. This output is held in the "mark" condition when the transmitter is disabled, idis, or when operating in local toopback mode. "Mark" is high, "space" is low. |  |  |  |

| OPO         | ×   | ×    |     | 0    | Output 0: General purpose output, or channel A request to send (RTSAN, active low). Can be deactivated on receive or transmit.                                                                                                                          |  |  |  |

| OPI         | ×   | ×    |     | 0    | Output 1: General purpose output, or channel B request to send (RTSBN, active low). Can be deactivated on receive or transmit.                                                                                                                          |  |  |  |

| OP2         | ×   | ×    | 1   | 0    | Output 2: General purpose output, or channel A transmitter 1X or 16X clock output, or channel A receiver 1X clock output.                                                                                                                               |  |  |  |

| OP3         | ×   |      | 1   | 0    | Output 3: General purpose output, or open drain, active low counter/limer output, or channel B transmitter 1X clock output, or channel B receiver 1X clock output                                                                                       |  |  |  |

| OP4         | ×   |      |     | 0    | Output 4: General purpose output, or channel Alopen drain, active low, RxRDYA/FFULLA output                                                                                                                                                             |  |  |  |

| OP5         | ×   |      |     | 0    | Output 5: General purpose output, or channel B open drain, active low, RxRDYB/FFULLB ou<br>put.                                                                                                                                                         |  |  |  |

| OPE         | ×   |      |     | 0    | Output 8: General purpose output, or channel A open drain, active low, TaRDYA output                                                                                                                                                                    |  |  |  |

| OP7         | ×   |      |     | 0    | Output 7: General purpose output, or channel B open drain, active low, TxRDYB output                                                                                                                                                                    |  |  |  |